Main data path, Main data path -3 – Altera DisplayPort MegaCore Function User Manual

Page 19

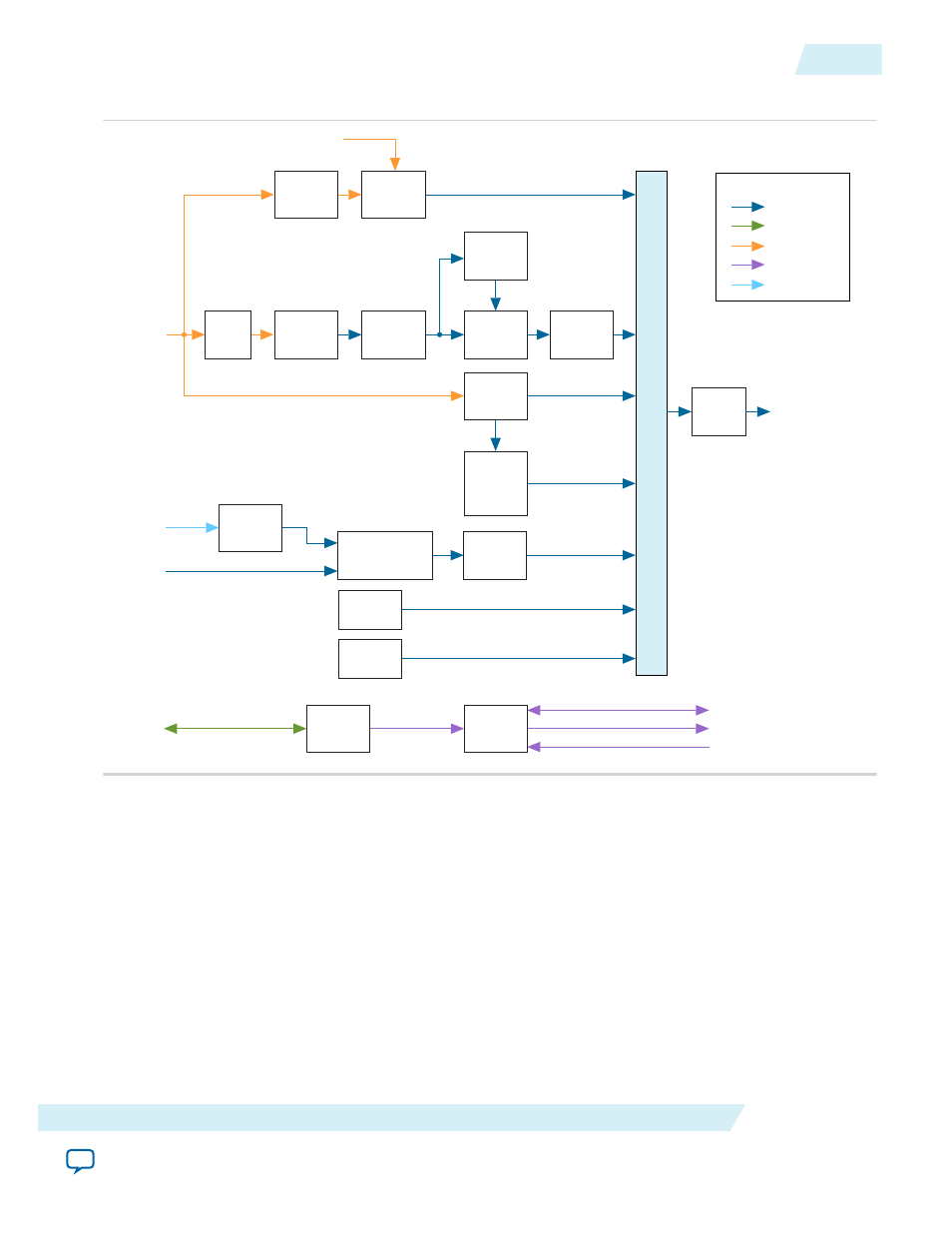

Figure 4-3: DisplayPort Source Functional Block Diagram

8B/10B

Encoder

Multiplexer

Fixed MSA

(txN_msa)

Avalon-MM

(tx_mgmt)

Bidirectional AUX Data

AUX Debug Stream

HPD

40-Bit (Quad Symbol) or

20-Bit (Dual Symbol)

Data to Transceiver

Secondary Data

(txN_ss)

Video Input

(txN_video_in)

Audio Stream

(txN_audio)

Gearbox

FIFO

Packetize

Throttle

Measure

Video

MSA

Generator

Blank Start

Generator

Video Data

Packet

Generator

Pixel

Steer

Secondary

Stream Encoder

DCFIFO

Controller

Registers

AUX

Controller

tx_ss_clk

clk

txN_vid_clk

aux_clk

txN_audio_clk

Legend

Audio

Encoder

DCFIFO

Training

Pattern 1

Training

Pattern 2

The source accepts a standard H-sync, V-sync, and data enable video stream for encoding. The IP core

latches and processes the video data before processing it using the

txN_video_in

input. N represents the

stream number:

tx_video_in

(Stream 0),

tx1_video_in

(Stream 1),

tx2_video_in

(Stream 2), and

tx3_video_in

(Stream 3).

The video data width supports 6 to 16 bits per color (bpc) and is user selectable. If you set the Pixel input

mode option to Dual or Quad, the video input can accept two or four pixels per clock, thereby extending

the pixel clock rate capability.

Main Data Path

The main data path consists of the packetizer, measurement, and blank generator paths. The IP core

multiplexes data from these three paths and outputs it through an 8B/10B encoder.

UG-01131

2015.05.04

Main Data Path

4-3

DisplayPort Source

Altera Corporation