Sink-supported dpcd locations, Sink-supported dpcd locations -33 – Altera DisplayPort MegaCore Function User Manual

Page 184

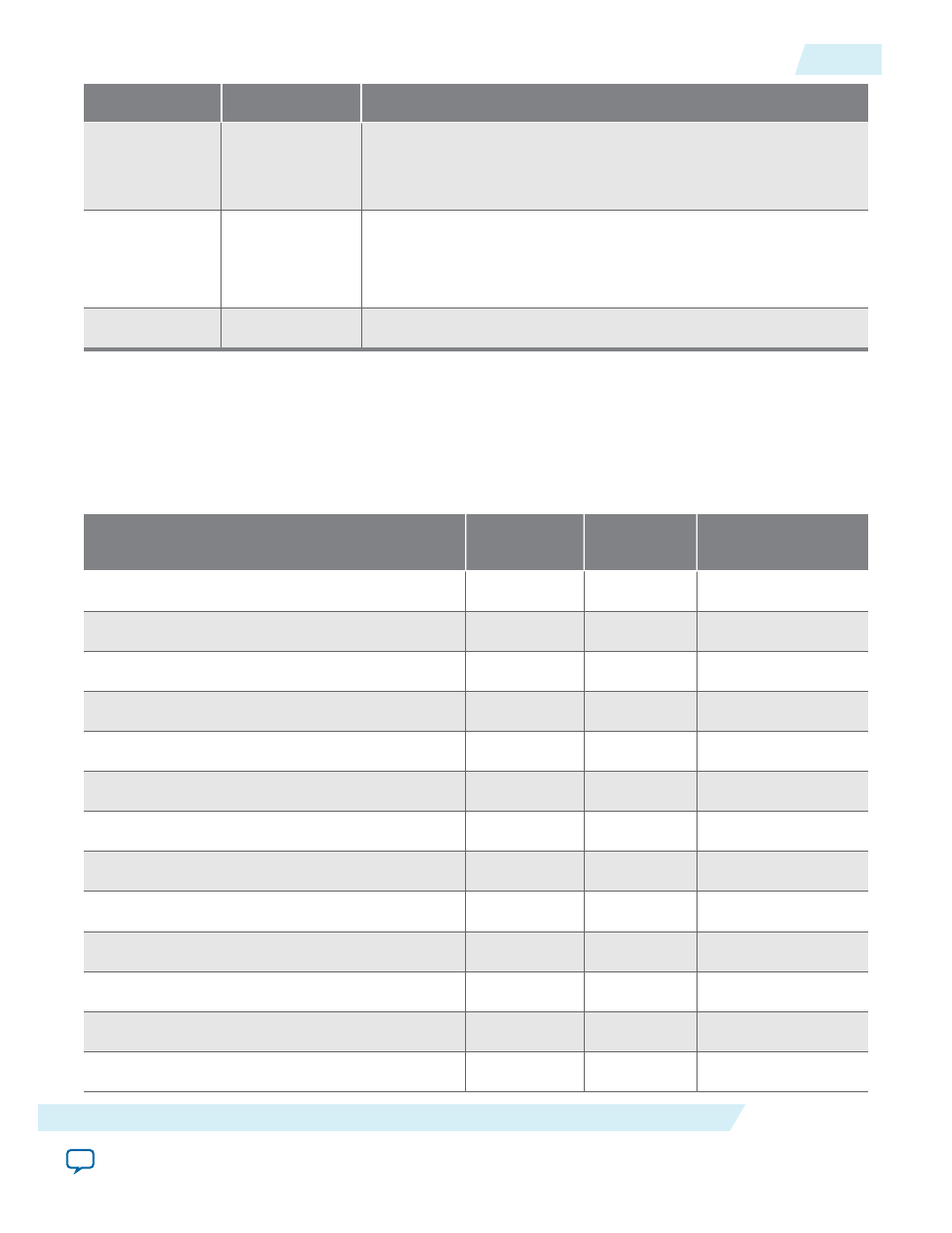

Bit

Bit Name

Function

12

HPD_IRQ

Writing this bit at 1 generates a 0.75-ms long HPD IRQ (low pulse).

This bit is WO.

To use this bit,

HPD_EN

must be 1.

11

HPD_EN

HPD logic level

0 = Deasserted (low)

1 = Asserted (high)

10:0

Unused

Sink-Supported DPCD Locations

The following table describes the DPCD locations (or location groups) that are supported in DisplayPort

sink instantiations.

Table 10-68: DPCD Locations

Location Name

Address

Without

Controller

With Controller

DPCD_REV

0×0000

Yes

Yes

MAX_LINK_RATE

0×0001

Yes

Yes

MAX_LANE_COUNT

0×0002

Yes

Yes

MAX_DOWNSPREAD

0×0003

Yes

Yes

NORP

0×0004

Yes

Yes

DOWNSTREAMPORT_PRESENT

0×0005

Yes

Yes

MAIN_LINK_CHANNEL_CODING

0×0006

Yes

Yes

DOWN_STREAM_PORT_COUNT

0×0007

Yes

Yes

RECEIVE_PORT0_CAP_0

0×0008

Yes

Yes

RECEIVE_PORT0_CAP_1

0×0009

Yes

Yes

RECEIVE_PORT1_CAP_0

0×000A

Yes

Yes

RECEIVE_PORT1_CAP_1

0×000B

Yes

Yes

I2C_SPEED_CONTROL

0×000C

—

Yes

UG-01131

2015.05.04

Sink-Supported DPCD Locations

10-33

DisplayPort Sink Register Map and DPCD Locations

Altera Corporation