Altera DisplayPort MegaCore Function User Manual

Page 93

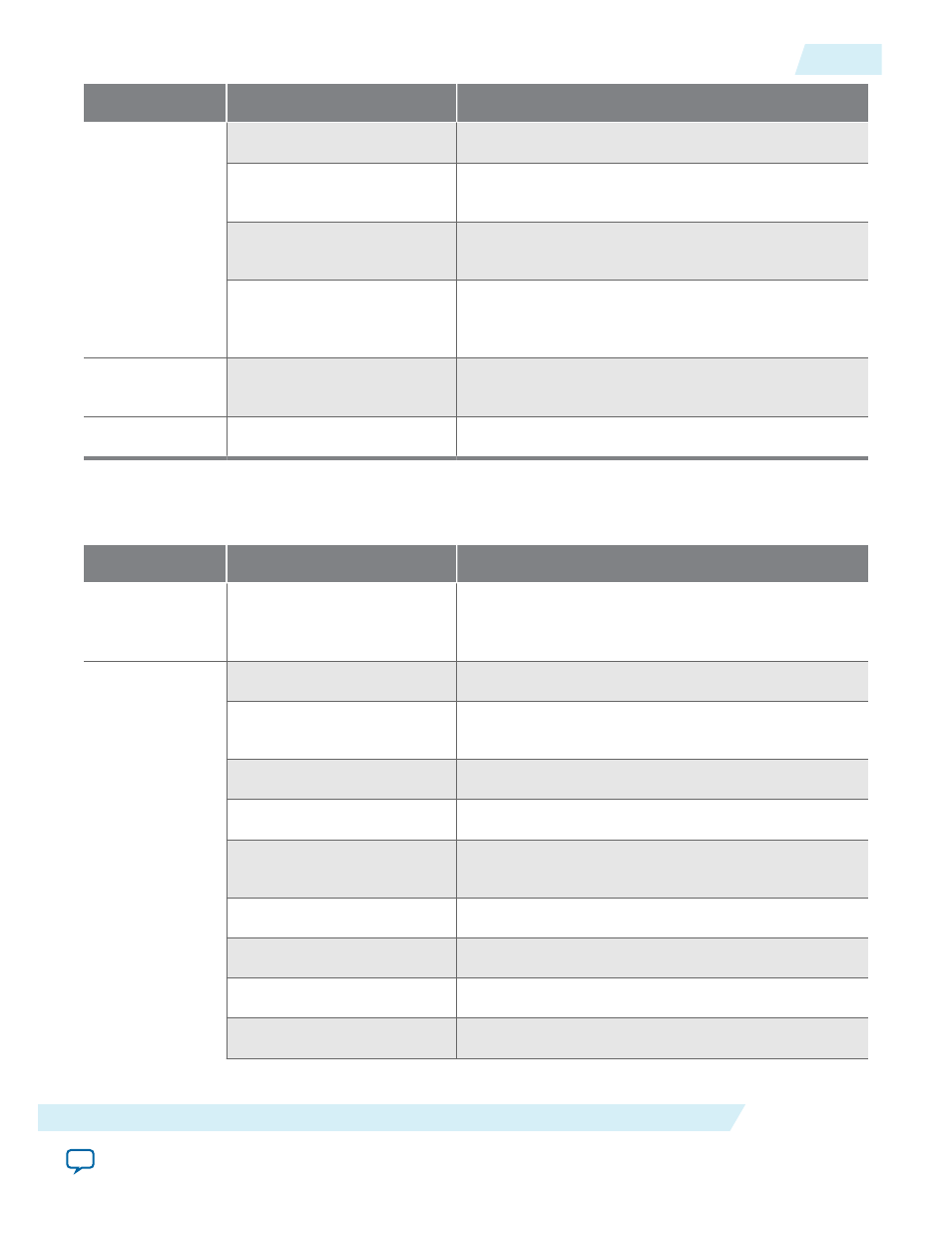

File Type

File

Description

Waveform

.do

files

all.do

Waveform that shows a combination of all waveforms.

reconfig.do

Waveform that shows the signals involved in reconfi‐

guring the transceiver.

rx_video_out.do

Waveform that shows the rx_video_out signals from

the DisplayPort IP core mapped to the CVI input.

tx_video_in.do

Waveform that shows the

tx_vid_v_sync

,

tx_vid_h_

sync

,

de

,

tx_vid_de

,

tx_vid_f

, and

tx_vid_

data[23:0]

signals at 256 pixels per line and 8 bpp, i.

Miscellaneous

files

readme.txt

Documentation for the simulation example.

edid_memory.hex

Initial content for the EDID ROM.

Table 7-2: Simulation Example Files for Arria V, Cyclone V, and Stratix V Devices

Files are named <prefix>_<name>.<extension> where <prefix> represents the device (av for Arria V devices, cv for

Cyclone V devices, and sv for Stratix V devices).

File Type

File

Description

System Verilog

HDL design

files

<prefix>

_dp_harness.sv

Top-level test harness.

Verilog HDL

design files

<prefix>

_dp_example.v

Design under test (DUT).

dp_mif_mappings.v

Table translating MIF mappings for transceiver

reconfiguration.

dp_analog_mappings.v

Table translating VOD and pre-emphasis settings.

reconfig_mgmt_hw_ctrl.v

Reconfiguration manager top-level.

reconfig_mgmt_write.v

Reconfiguration manager FSM for a single write

command.

clk_gen.v

Clock generation file.

freq_check.sv

Top-level file for the frequency checker.

rx_freq_check.sv

RX frequency checker.

tx_freq_check.sv

TX frequency checker.

UG-01131

2015.05.04

Copy the Simulation Files to Your Working Directory

7-5

DisplayPort IP Core Simulation Example

Altera Corporation