Altera DisplayPort MegaCore Function User Manual

Page 194

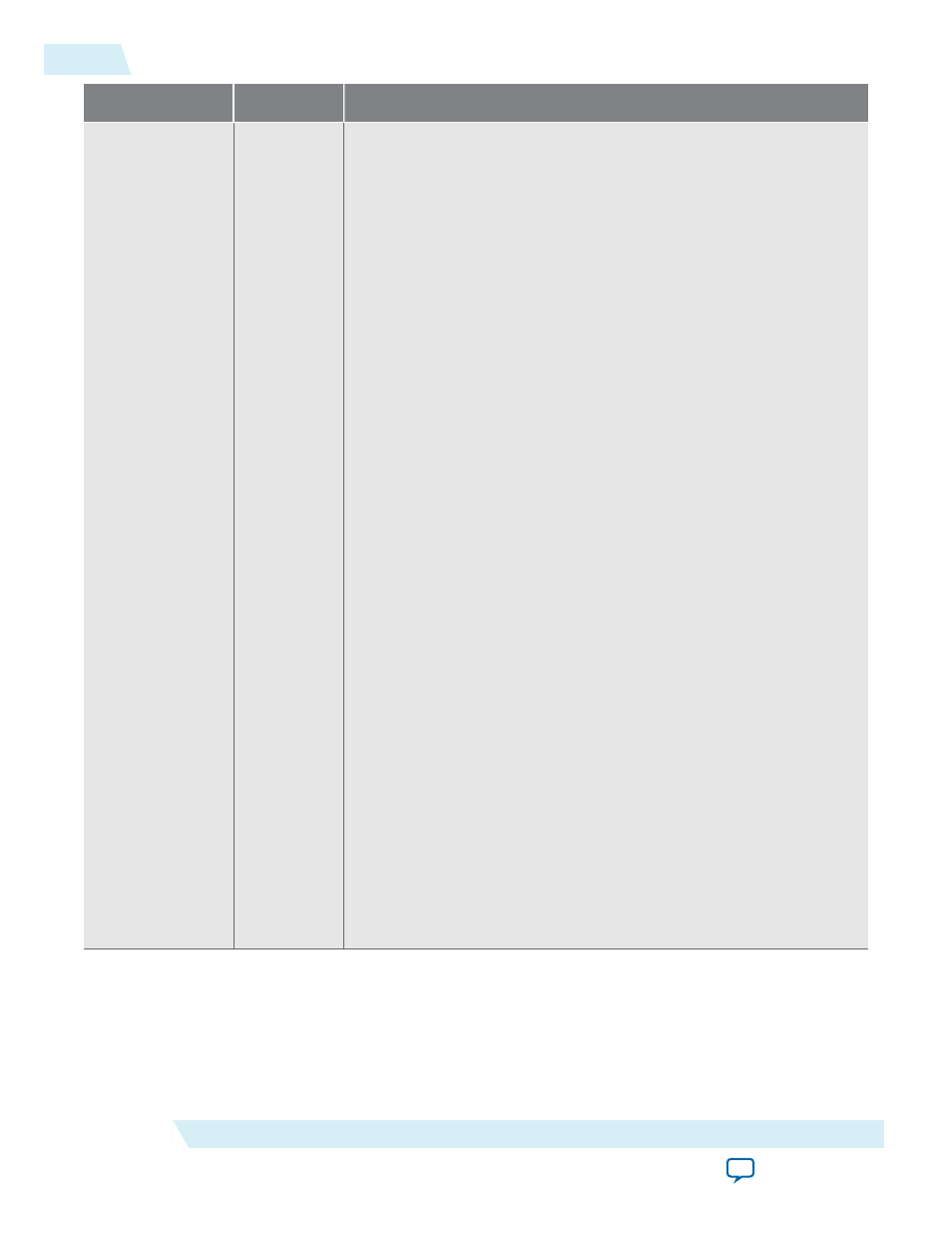

Date

Version

Changes

June 2014

2014.06.30

• Native PHY is removed from the IP core; included information

about how to instantiate the PHY outside the DisplayPort IP core.

• Updated the source and sink block diagrams.

• Updated the source and sink register map information.

• Added new sink register bits:

•

LQA ACTIVE

•

PHY_SINK_TEST_LANE_SEL

•

PHY_SINK_TEST_LANE_EN

•

AUX_IRQ_EN

•

TX_STROBE

•

DPRX_AUX_STATUS

bits

•

DPRX_AUX_I2C0

bits

•

DPRX_AUX_I2C0

bits

•

DPRX_AUX_HPD

bits

• Removed these sink register bits:

•

HPD_IRQ

•

HPD_EN

•

DPRX_AUX_IRQ_EN

bits

• Added a new source register bit:

•

VTOTAL

• Added source TX transceiver interface signals

• Removed these source signals:

•

xcvr_refclk

•

tx_serial_data

•

xcvr_reconfig

• Added sink audio and RX transceiver interface signals.

• Removed these sink signals:

•

xcvr_refclk

•

rx_serial_data

•

xcvr_reconfig

• Added information about Transceiver Reconfiguration Interface for

source and sink.

• Added information about single clock reference (135MHz) for

source and sink.

• Added information about Bitec HSMC DisplayPort daughter card

in the Hardware Demonstration chapter.

• Updated the API reference.

A-4

Document Revision History

UG-01131

2015.05.04

Altera Corporation

Additional Information