Altera DisplayPort MegaCore Function User Manual

Page 24

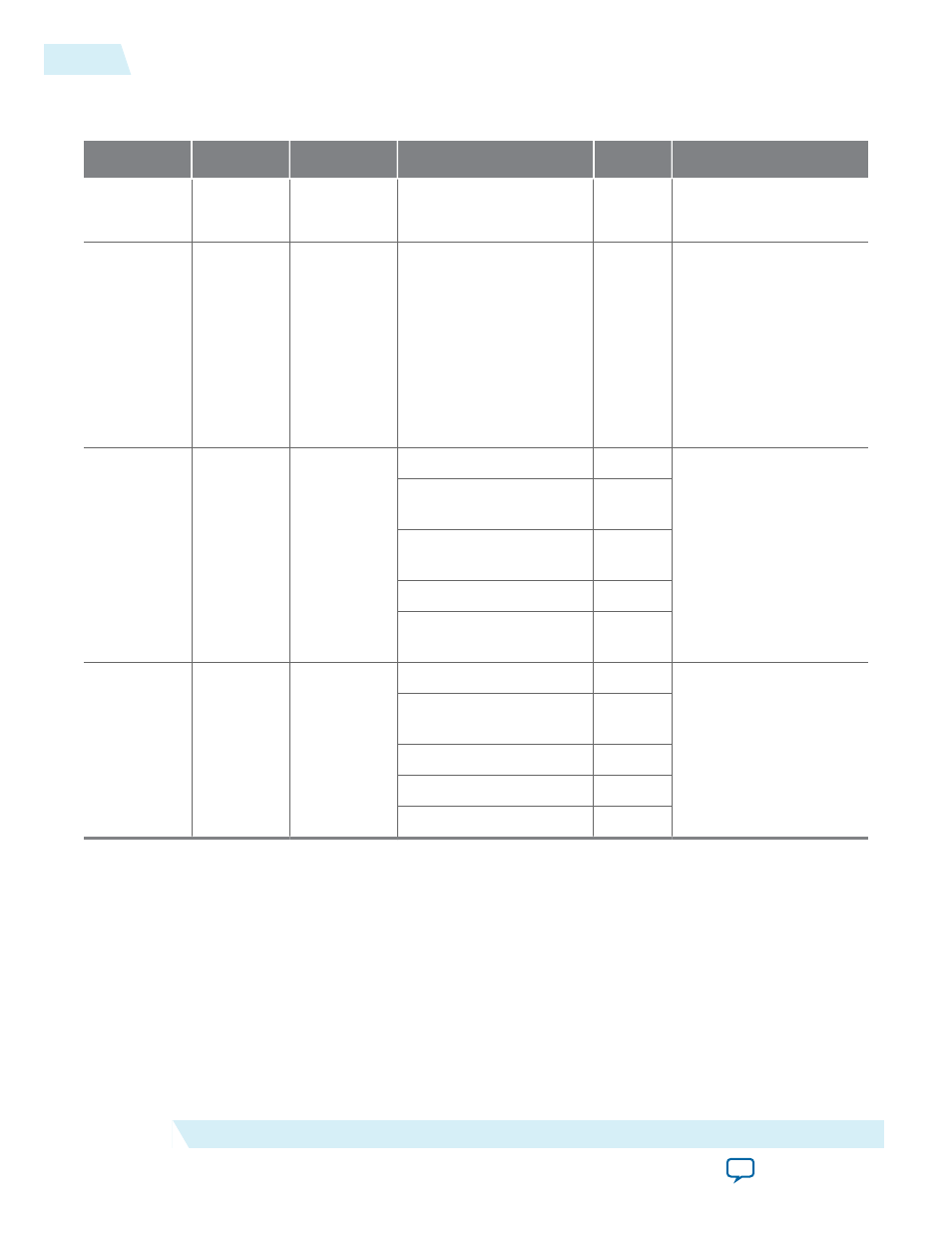

Table 4-3: Transceiver Management Interface

n

is the number of TX lanes.

Interface

Port Type

Clock Domain

Port

Direction

Description

xcvr_

mgmt_clk

Clock

N/A

xcvr_mgmt_clk

Input

Transceiver

management clock

clk_cal

Clock

N/A

clk_cal

Input

A 50-MHz calibration

clock input. This clock

must be synchronous

to the clock used for

the Transceiver

Reconfiguration block

(

xvcr_mgmt_clk

),

external to the Display‐

Port sink.

tx_

analog_

reconfig

Conduit

xcvr_mgmt_

clk

tx_vod[2n - 1:0]

Output

Transceiver analog

reconfiguration

handshaking

tx_emp[2n - 1:0]

Outp

ut

tx_analog_reconfig_req

Outp

ut

tx_analog_reconfig_ack

Input

tx_analog_reconfig_

busy

Input

tx_

reconfig

Conduit

xcvr_mgmt_

clk

tx_link_rate[1:0]

Output

Transceiver link rate

reconfiguration

handshaking

tx_link_rate_

8bits[7:0]

Outp

ut

tx_reconfig_req

Input

tx_reconfig_ack

Input

tx_reconfig_busy

Input

Note: Value of tx_link_rate[1:0]: 0=1.62Gbps, 1=2.70Gbps, 2=5.40Gbps; value of tx_link_rate_8bits[7:0]:

0×06=1.62Gbps, 0×0a=2.70Gbps, 0×14=5.40Gbps.

Note: For devices using a 50-MHz

xcvr_mgmt_clk

clock, connect the same clock directly also to the

clk_cal

signal. For devices using a 100-MHz

xcvr_mgmt_clk

clock, connect the same clock to

clk_cal

signal through a by-2 divider.

4-8

Source Interfaces

UG-01131

2015.05.04

Altera Corporation

DisplayPort Source