Altera DisplayPort MegaCore Function User Manual

Page 73

Parameters

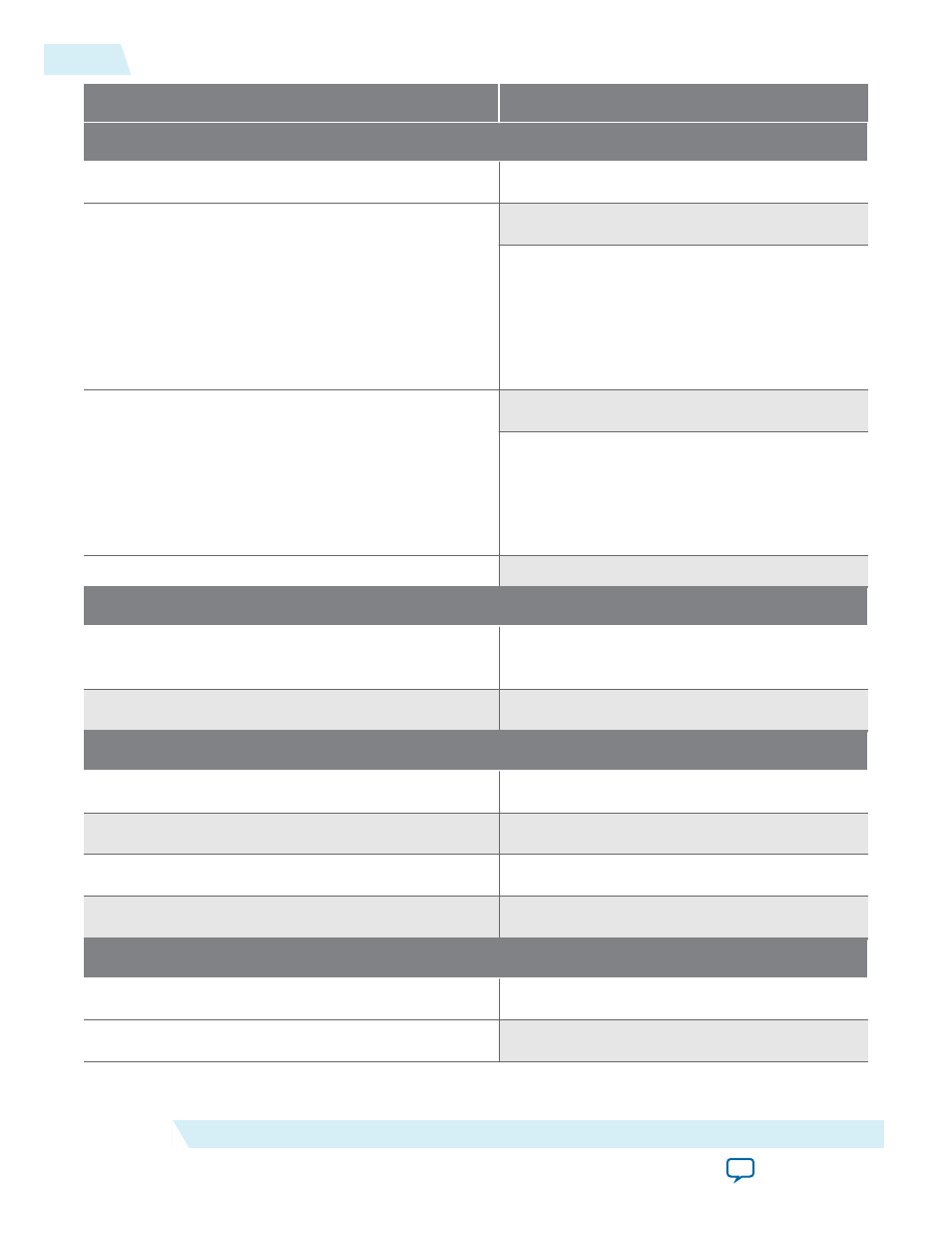

Single Reference Clock Settings

Datapath Options

Enable standard PCS

On

Number of data channels

1, 2 or 4

Note: If you select 1 or 2, you must

instantiate the PHY instance multiple

times for all data channels as per

maximum lane count parameter.

These values are for non-bonded

mode.

Bonding mode

×1* or ×N

Note: If you select ×1, you must instantiate

the PHY instance multiple times for

all data channels as per maximum

lane count parameter. This value is

for non-bonded mode.

Enable simplified data interface

PMA

Data rate

2700 Mbps (when TX maximum link rate = 2.7

Gbps)

TX local clock division factor

2 (when TX/RX maximum link rate = 2.7Gbps)

TX PMA

Enable TX PLL dynamic reconfiguration

On

Number of TX PLLs

1

Main TX PLL logical index

0

Number of TX PLL reference clock

1

TX PLL0

PLL type

CMU

Reference clock frequency

135 MHz

6-12

Transceiver and Clocking

UG-01131

2015.05.04

Altera Corporation

DisplayPort IP Core Hardware Demonstration