Altera DisplayPort MegaCore Function User Manual

Page 78

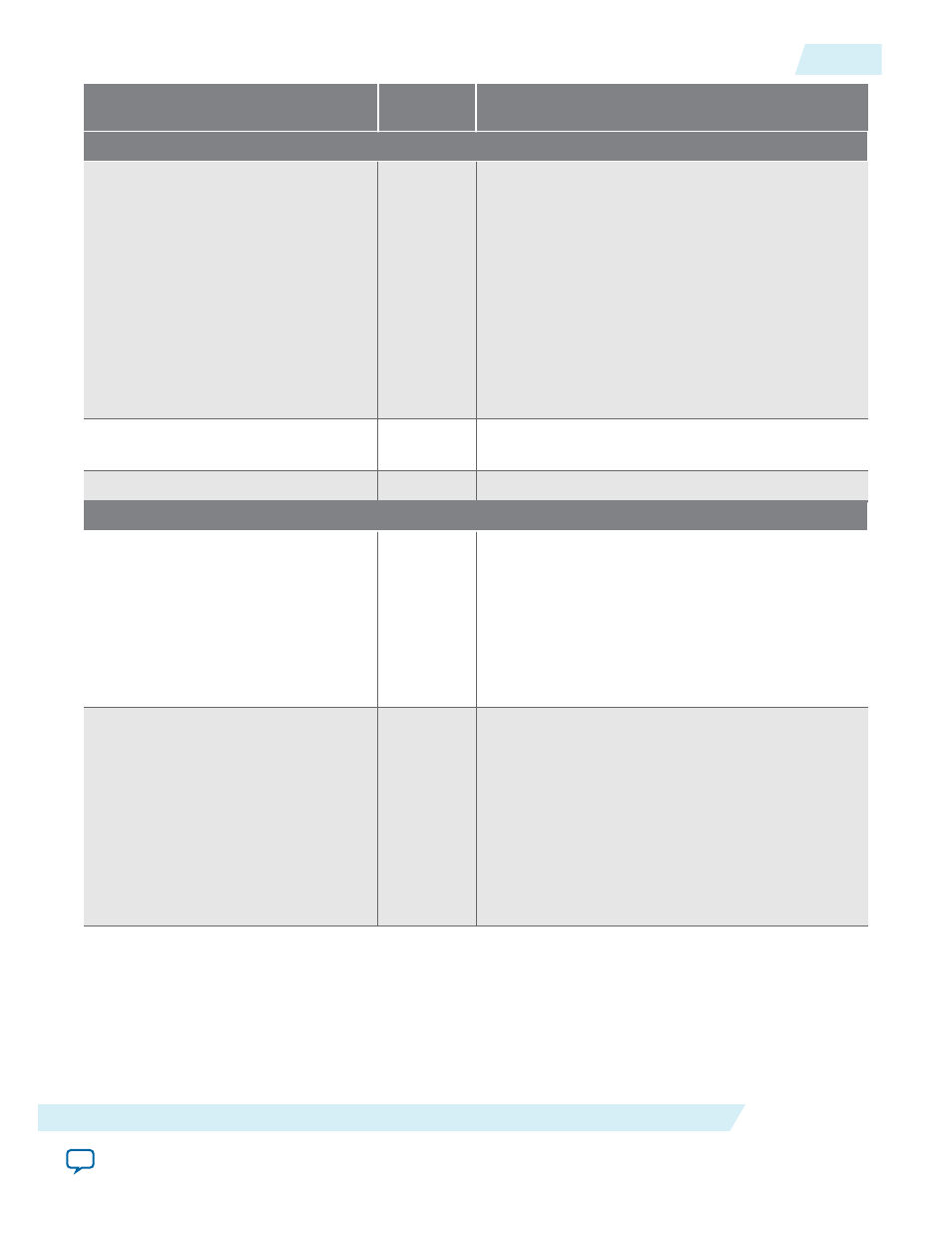

Bitec DP Card Signal

Bitec Card I/

O

Description

HSMC Connector J4A

HSMA_RX_P[3..0]

,

HSMA_RX_N[3..0]

Output

RX Main Link lane[3..0] differential signals.

The demonstration software sets the RX Main Link

redriver’s EQ settings. Refer to

main.c

provided in

the demonstration software directory.

Depending on the channel condition, you may want

to try various combinations of the EQ, VOD/pre-

emphasis settings to achieve optimal link perform‐

ance.

I

2

C address for RX Main Link redriver: write=0×58,

read=0×59.

SCL_CTL

,

SDA_CTL

I/O

I

2

C bus signals to configure the TX and RX Main

Link redriver EQ, VOD/pre-emphasis settings.

TDO_TDI

Not used

—

HSMC Connector J4B

RX_CAD

Input

Cable Adapter Detect.

This is used to select DisplayPort mode or TMDS

mode in the Main Link redrivers.

0=DP mode, 1=TMDS mode.

The demonstration design selects the DisplayPort

mode(RX_CAD=0).

RX_SENSE_P

Output

The sink uses this to detect the presence of the

source device.

• 0=Source DisplayPort cable is plugged.

• 1=Source DisplayPort cable is not plugged.

When connecting this to the sink

rx_cable_detect

(active high) input, inverted signal should be used.

In the demonstration design, the

rx_cable_detect

input is set to 1 in the RTL.

UG-01131

2015.05.04

Required Hardware

6-17

DisplayPort IP Core Hardware Demonstration

Altera Corporation