Altera JESD204B IP User Manual

Page 108

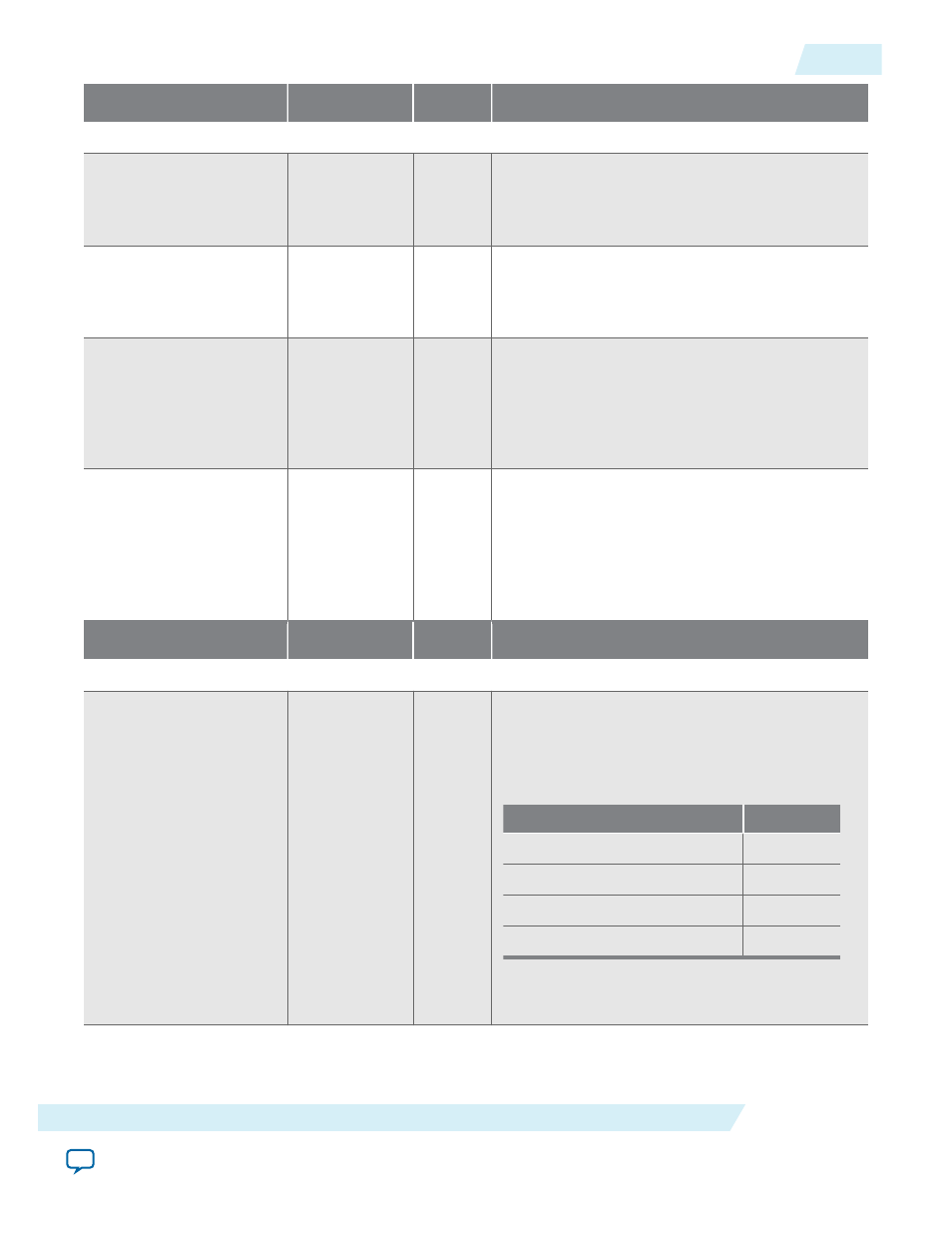

Signal

Clock Domain

Direction

Description

Between Avalon- ST and Transport Layer

jesd204_rx_

dataout[(OUTPUT_BUS_

WIDTH)-1:0]

rxframe_clk

Output

RX data to the Avalon-ST source interface. The

transport layer arranges the data in a specific

order, as illustrated in the cases listed in

jesd204_rx_

controlout[CONTROL_

BUS_WIDTH -1:0]

rxframe_clk

Output

RX control data to the Avalon-ST source

interface. The transport layer arranges the data in

a specific order, as illustrated in the cases listed in

jesd204_rx_data_

valid

rxframe_clk

Output

Indicates whether the data from the transport

layer to the Avalon-ST sink interface is valid or

invalid.

• 0—data is invalid

• 1—data is valid

jesd204_rx_data_

ready

rxframe_clk

Input

Indicates that the Avalon-ST sink interface is

ready to accept data from the transport layer.

• 0—Avalon-ST sink interface is not ready to

receive data

• 1—Avalon-ST sink interface is ready to receive

data

Signal

Clock Domain

Direction

Description

Between Transport Layer and DLL

jesd204_rx_link_

datain[(L*32)-1:0]

rxlink_clk

Input

Indicates received data from the DLL to the

transport layer, where four octets are packed into

a 32-bit data width per lane. The data format is

big endian. The table below illustrates the data

mapping for L = 4:

jesd204_rx_link_datain [x:y]

Lane

[31:0]

0

[63:32]

1

[95:64]

2

[127:96]

3

Connect this signal to the RX DLL

jesd204_rx_

link_data[]

output pin.

UG-01142

2015.05.04

RX Path

5-27

JESD204B IP Core Design Guidelines

Altera Corporation