Altera JESD204B IP User Manual

Page 5

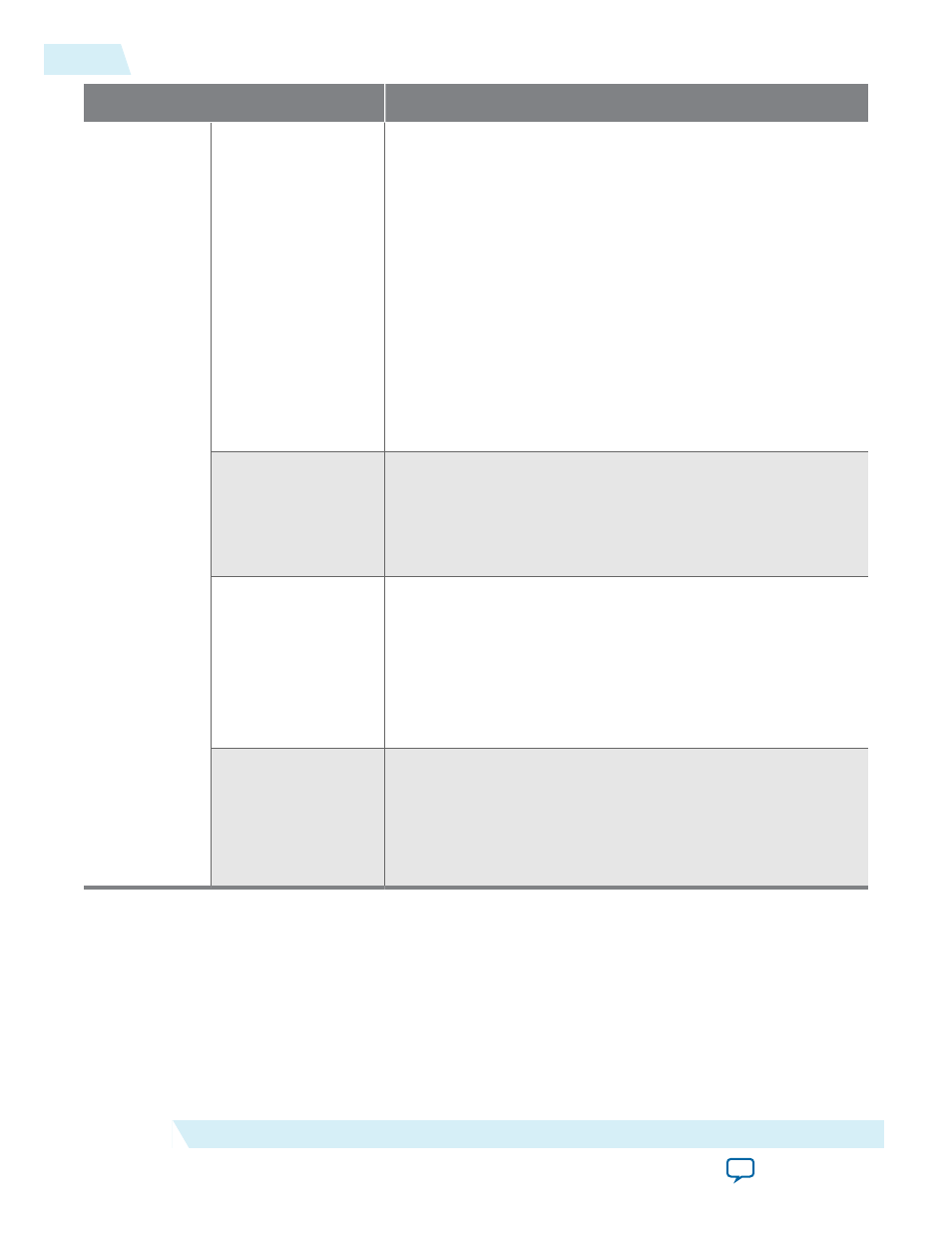

Item

Description

IP Core

Information

Core Features

• Run-time configuration of parameters L,M, and F

• Data rates up to 12.5 gigabits per second (Gbps)

• Single or multiple lanes (up to 8 lanes per link)

• Serial lane alignment and monitoring

• Lane synchronization

• Modular design that supports multidevice synchronization

• MAC and PHY partitioning

• Deterministic latency support

• 8B/10B encoding

• Scrambling/Descrambling

• Avalon

®

Streaming (Avalon-ST) interface for transmit and

receive datapaths

• Avalon Memory-Mapped (Avalon-MM) interface for

Configuration and Status registers (CSR)

• Dynamic generation of simulation testbench

Typical Application

• Wireless communication equipment

• Broadcast equipment

• Military equipment

• Medical equipment

• Test and measurement equipment

Device Family Support • Cyclone

®

V FPGA device families

• Arria

®

V FPGA device families

• Arria V GZ FPGA device families

• Arria 10 FPGA device families

• Stratix

®

V FPGA device families

Refer to the device support table andWhat’s New in Altera IP

page of the Altera website for detailed information.

Design Tools

• Qsys parameter editor in the Quartus II software for design

creation and compilation

• TimeQuest timing analyzer in the Quartus II software for

timing analysis

• ModelSim

®

-Altera, Aldec Riviera-Pro, VCS/VCS MX, and

NCSim software for design simulation or synthesis

Related Information

•

•

1-2

JESD204B IP Core Quick Reference

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Quick Reference