Altera JESD204B IP User Manual

Page 12

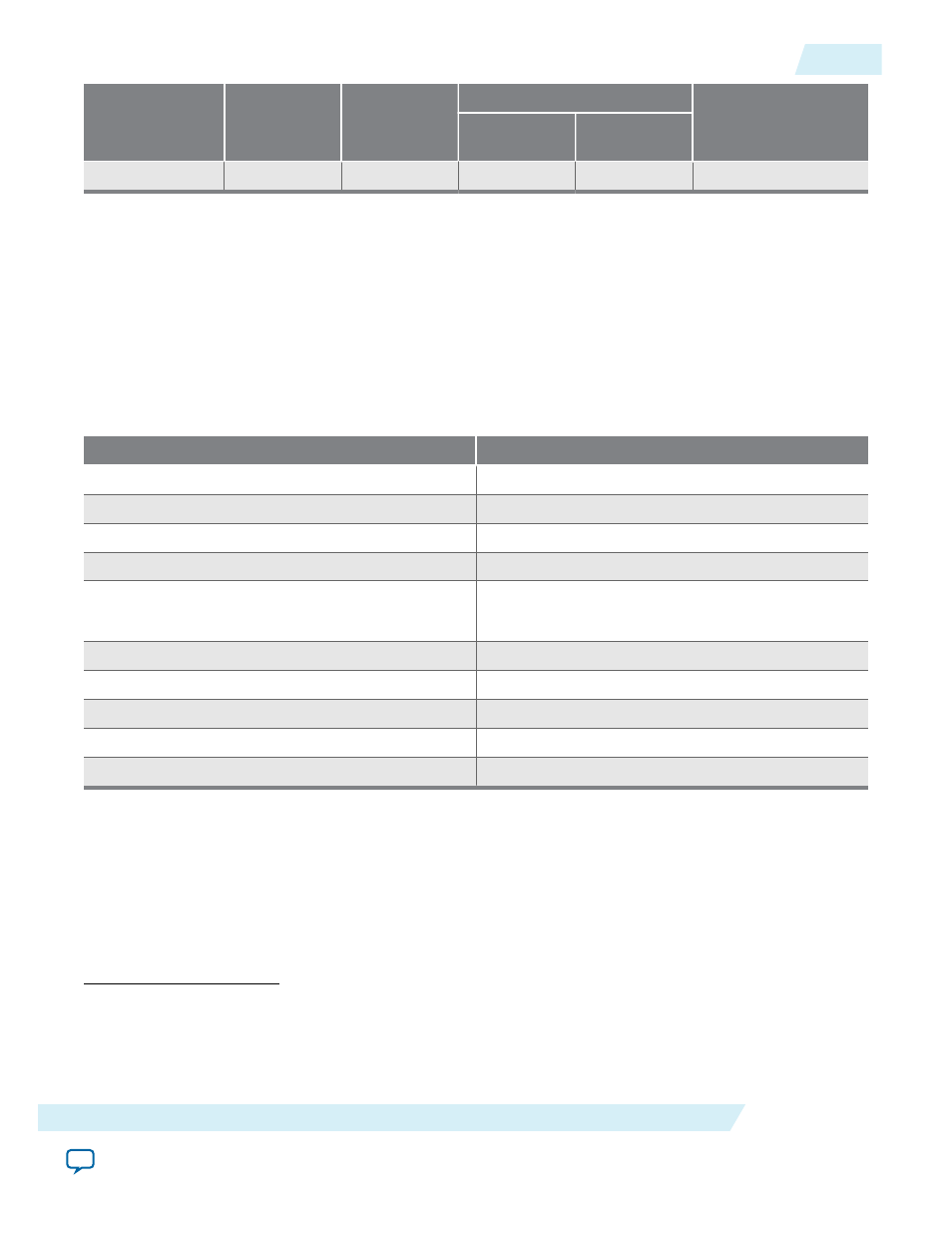

Device Family

PMA Speed

Grade

FPGA Fabric

Speed Grade

Data Rate

Link Clock F

MAX

(MHz)

Enable Hard

PCS (Gbps)

Enable Soft PCS

(Gbps)

(3)

Stratix V

3

1, 2, 3, or 4

2.0 to 8.5

2.0 to 8.5

312.50

The following table lists the resources and expected performance of the JESD204B IP core. These results

are obtained using the Quartus II software targeting the following Altera FPGA devices:

• Cyclone V : 5CGTFD9E5F31I7

• Arria V : 5AGXFB3H4F35C5

• Arria V GZ : 5AGZME5K2F40C3

• Arria 10 : 10AX115H2F34I2SGES

• Stratix V : 5SGXEA7H3F35C3

All the variations for resource utilization are configured with the following parameter settings:

Table 2-4: Parameter Settings To Obtain the Resource Utilization Data

Parameter

Setting

JESD204B Wrapper

Base and PHY

JESD204B Subclass

1

Data Rate

5 Gbps

PCS Option

Enabled Hard PCS

PLL Type

• ATX (for 10 series devices)

• CMU (for V series devices)

Bonding Mode

Non-bonded

Reference Clock Frequency

125.0 MHz

Octets per frame (F)

1

Enable Scrambler (SCR)

Off

Enable Error Code Correction (ECC_EN)

Off

(3)

Select Enable Soft PCS to achieve maximum data rate. For the TX IP core, enabling soft PCS incurs an

additional 3–8% increase in resource utilization. For the RX IP core, enabling soft PCS incurs an additional

10–20% increase in resource utilization.

(5)

When using Soft PCS mode at 12.5 Gbps, the timing margin is very limited. You are advised to enable

HIGH fitter effort, register duplication, and register retiming to improve timing performance.

UG-01142

2015.05.04

Performance and Resource Utilization

2-7

About the JESD204B IP Core

Altera Corporation