Altera JESD204B IP User Manual

Page 69

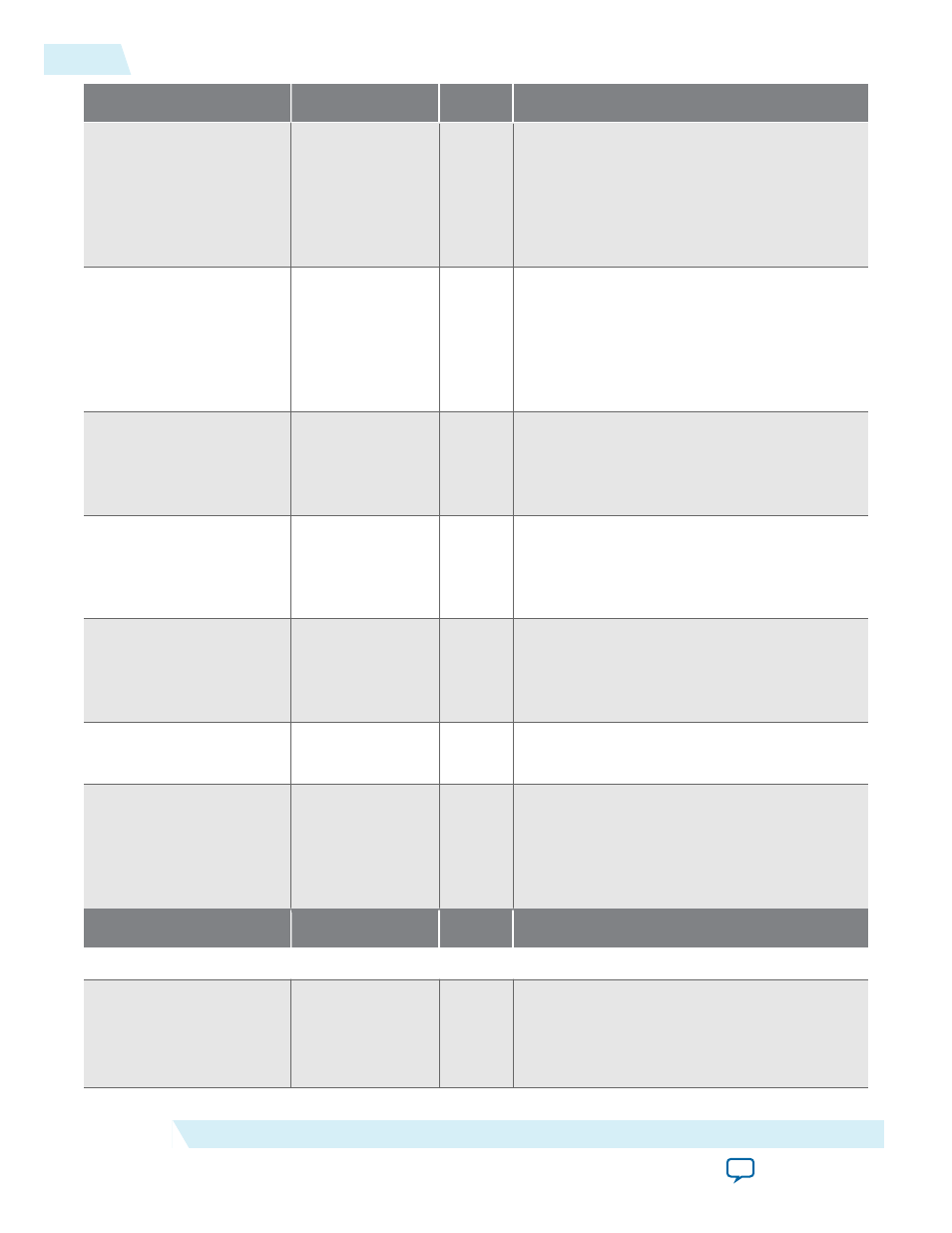

Signal

Width

Direction

Description

jesd204_tx_avs_

chipselect

1

Input

When this signal is present, the slave port

ignores all Avalon-MM signals unless this

signal is asserted. This signal must be used in

combination with read or write. If the Avalon-

MM bus does not support chip select, you are

recommended to tie this port to 1.

jesd204_tx_avs_

address[]

8

Input

For Avalon-MM slave, the interconnect

translates the byte address into a word address

in the address space so that each slave access is

for a word of data. For example, address = 0

selects the first word of the slave and address =

1 selects the second word of the slave.

jesd204_tx_avs_

writedata[]

32

Input

32-bit data for write transfers. The width of

this signal and the

jesd204_tx_avs_

readdata[31:0]

signal must be the same if

both signals are present

jesd204_tx_avs_read

1

Input

This signal is asserted to indicate a read

transfer. This is an active high signal and

requires the

jesd204_tx_avs_

readdata[31:0]

signal to be in use.

jesd204_tx_avs_write

1

Input

This signal is asserted to indicate a write

transfer. This is an active high signal and

requires the

jesd204_tx_avs_

writedata[31:0]

signal to be in use.

jesd204_tx_avs_

readdata[]

32

Output

32-bit data driven from the Avalon-MM slave

to master in response to a read transfer.

jesd204_tx_avs_

waitrequest

1

Output

This signal is asserted by the Avalon-MM slave

to indicate that it is unable to respond to a

read or write request. The JESD204B IP core

ties this signal to 0 to return the data in the

access cycle.

Signal

Width

Direction

Description

JESD204 Interface

sysref

1

Input

SYSREF signal for JESD204B Subclass 1

implementation.

For Subclass 0 and Subclass 2 mode, tie-off

this signal to 0.

4-32

Transmitter

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description