Example feature: dynamic reconfiguration, Dynamic reconfiguration operation, Example feature: dynamic reconfiguration -49 – Altera JESD204B IP User Manual

Page 130

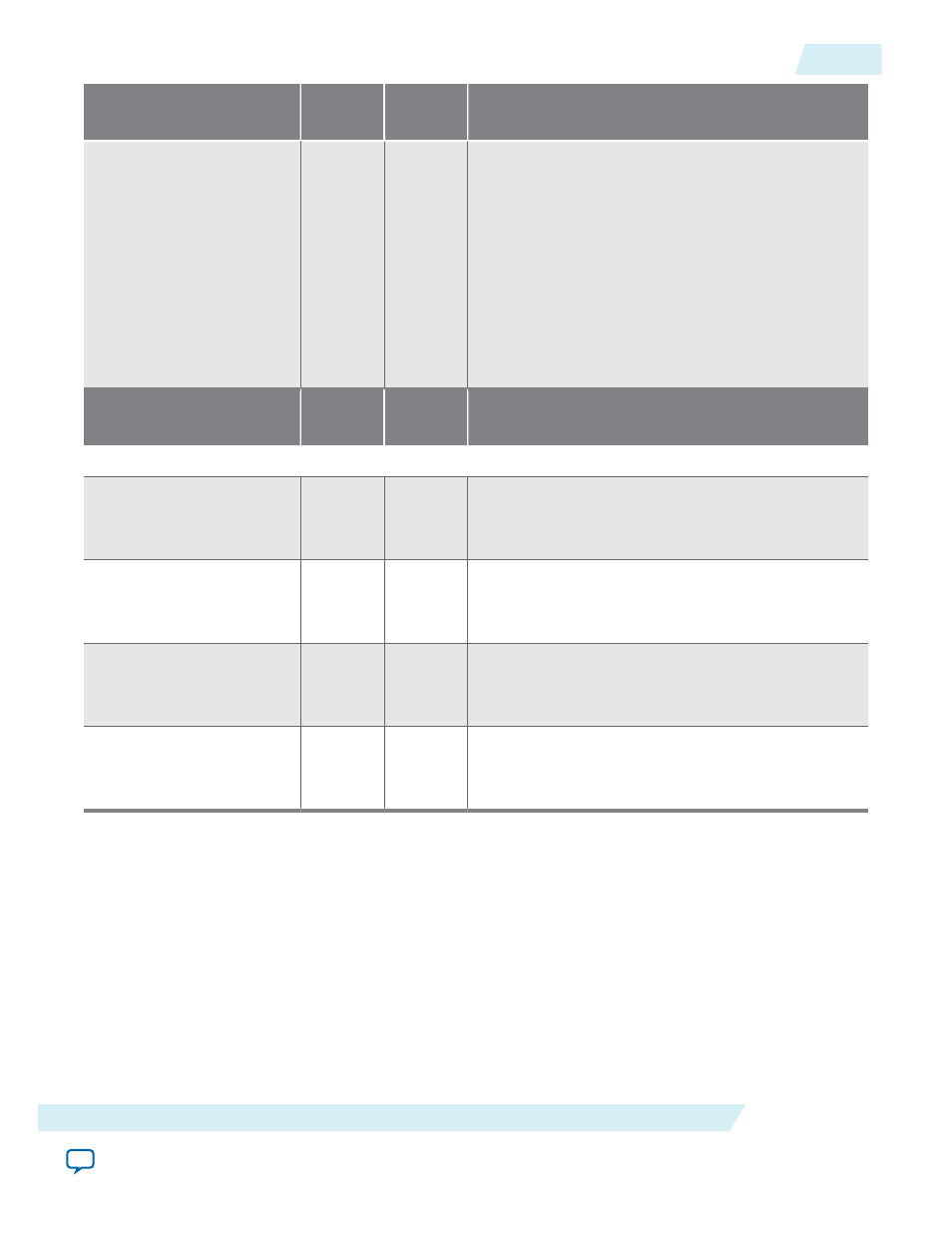

Signal

Clock

Domain

Direction

Description

test_mode[3:0]

frame_

clk

Input

Specifies the operation mode.

• 0000—Normal mode. The design example takes

data from the Avalon-ST source.

• 1000—Test mode. The design example generates

alternate checkerboard data pattern.

• 1001—Test mode. The design example generates

ramp wave data pattern.

• 1010—Test mode. The design example generates

the PRBS data pattern.

• Others—Reserved

Signal

Clock

Domain

Direction

Description

Status

rx_is_lockedtodata

[LINK*L-1:0]

device_

clk

Output

Asserted to indicate that the RX CDR PLL is locked

to the RX data and the RX CDR has changed from

LTR to LTD mode.

data_error [LINK-1:0]

frame_

clk

Output

Asserted to indicate that the pattern checker has

found a mismatch in the received data and the

expected data. One error signal per pattern checker.

jesd204_tx_int[LINK-

1:0]

link_clk

Output

Interrupt pin for the JESD204B IP core (TX). The

interrupt signal is asserted when an error condition

or synchronization request is detected.

jesd204_rx_int[LINK-

1:0]

link_clk

Output

Interrupt pin for the JESD204B IP core (RX). The

interrupt signal is asserted when an error condition

or synchronization request is detected.

Example Feature: Dynamic Reconfiguration

The JESD204B IP core design example demonstrates dynamic (run-time) reconfiguration of either the

LMF or data rate, at any one time.

Dynamic Reconfiguration Operation

The dynamic reconfiguration feature implements various reconfiguration controller modules such as PLL

reconfiguration, Transceiver Reconfiguration Controller, SPI master, and JESD204B IP core Avalon-MM

slave. These modules connect to the control unit through the Avalon-MM interface. You can control the

reconfiguration using the

reconfig

,

runtime_lmf

, and

runtime_datarate

input ports exposed at control

unit interface.

UG-01142

2015.05.04

Example Feature: Dynamic Reconfiguration

5-49

JESD204B IP Core Design Guidelines

Altera Corporation