Altera JESD204B IP User Manual

Page 31

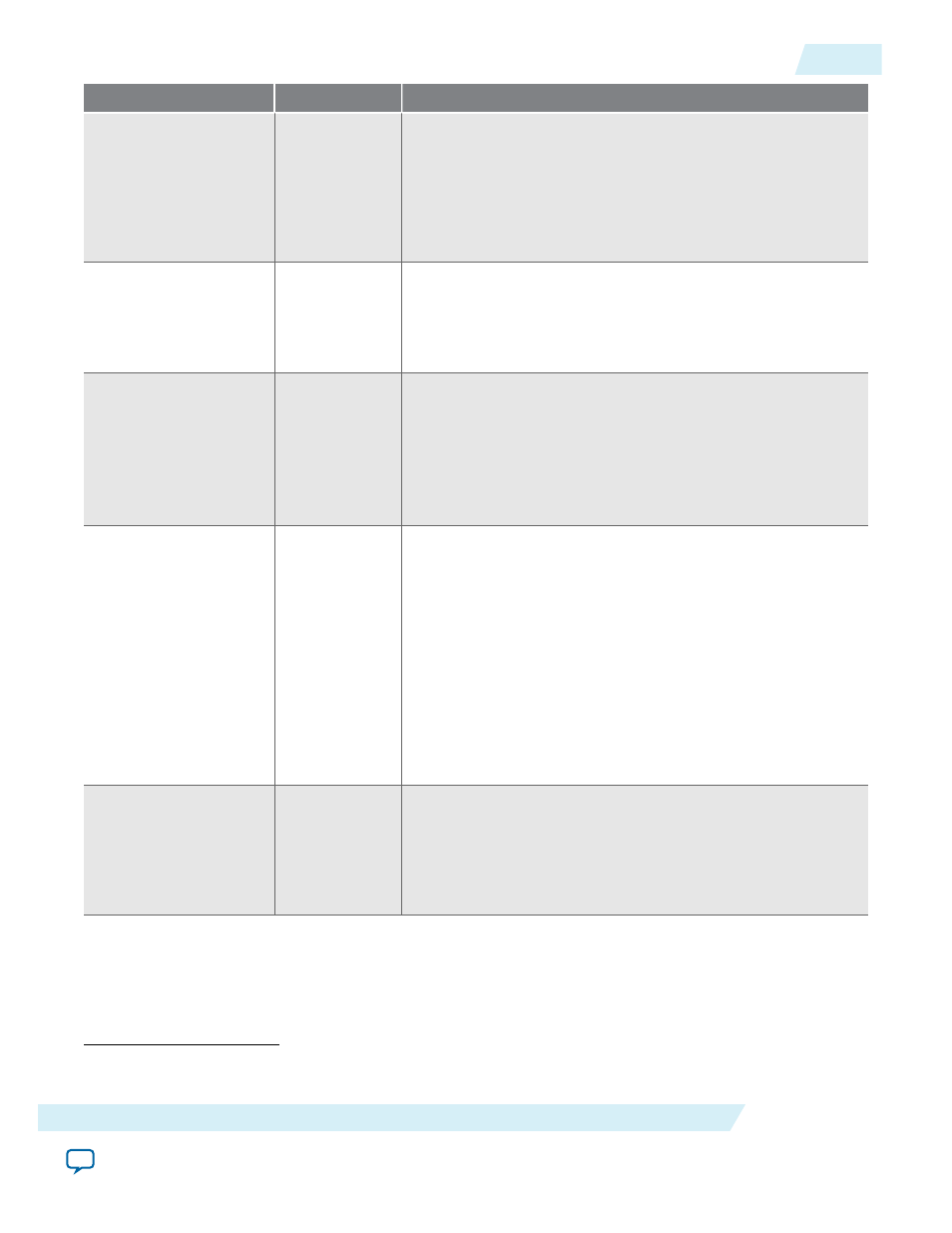

Parameter

Value

Description

Data Path

• Receiver

• Transmitter

• Duplex

Select the operation modes. This selection enables or disables

the receiver and transmitter supporting logic.

• RX—instantiates the receiver to interface to the ADC.

• TX—instantiates the transmitter to interface to the DAC.

• Duplex—instantiates the receiver and transmitter to

interface to both the ADC and DAC.

JESD204B Subclass

• 0

• 1

• 2

Select the JESD204B subclass modes.

• 0—Set subclass 0

• 1—Set subclass 1

• 2—Set subclass 2

Data Rate

1.0–12.5

Set the data rate for each lane.

(12)

• Cyclone V—1.0 Gbps to 5.0 Gbps

• Arria V—1.0 Gbps to 6.55 Gbps

• Arria V GZ—2.0 Gbps to 9.9 Gbps

• Arria 10—2.0 Gbps to 12.5 Gbps

• Stratix V—2.0 Gbps to 12.5 Gbps

PCS Option

• Enabled

Hard PCS

• Enabled Soft

PCS

Select the PCS modes.

• Enabled Hard PCS—utilize Hard PCS components. Select

this option to minimize resource utilization with data rate

that supports up to the limitation of the Hard PCS.

Note: For this setting, you will utilize 8G PCS mode

with 20 bits PMA width and 32 bits PCS width.

• Enabled Soft PCS—utilize Soft PCS components. Select this

option to allow higher supported data rate but increase in

resource utilization.

Note: For this setting, you will utilize 10G PCS mode

with 40 bits PMA width and 40 bits PCS width.

PLL Type

• CMU

• ATX

Select the Phase-Locked Loop (PLL) types, depending on the

FPGA device family.

• Cylone V—CMU

• Arria V—CMU

• Stratix V—CMU, ATX

(12)

The maximum data rate is limited by different device speed grade, transceiver PMA speed grade, and

PCS options. Refer to

for the maximum data rate support.

UG-01142

2015.05.04

JESD204B IP Core Parameters

3-17

Getting Started

Altera Corporation