Altera JESD204B IP User Manual

Page 114

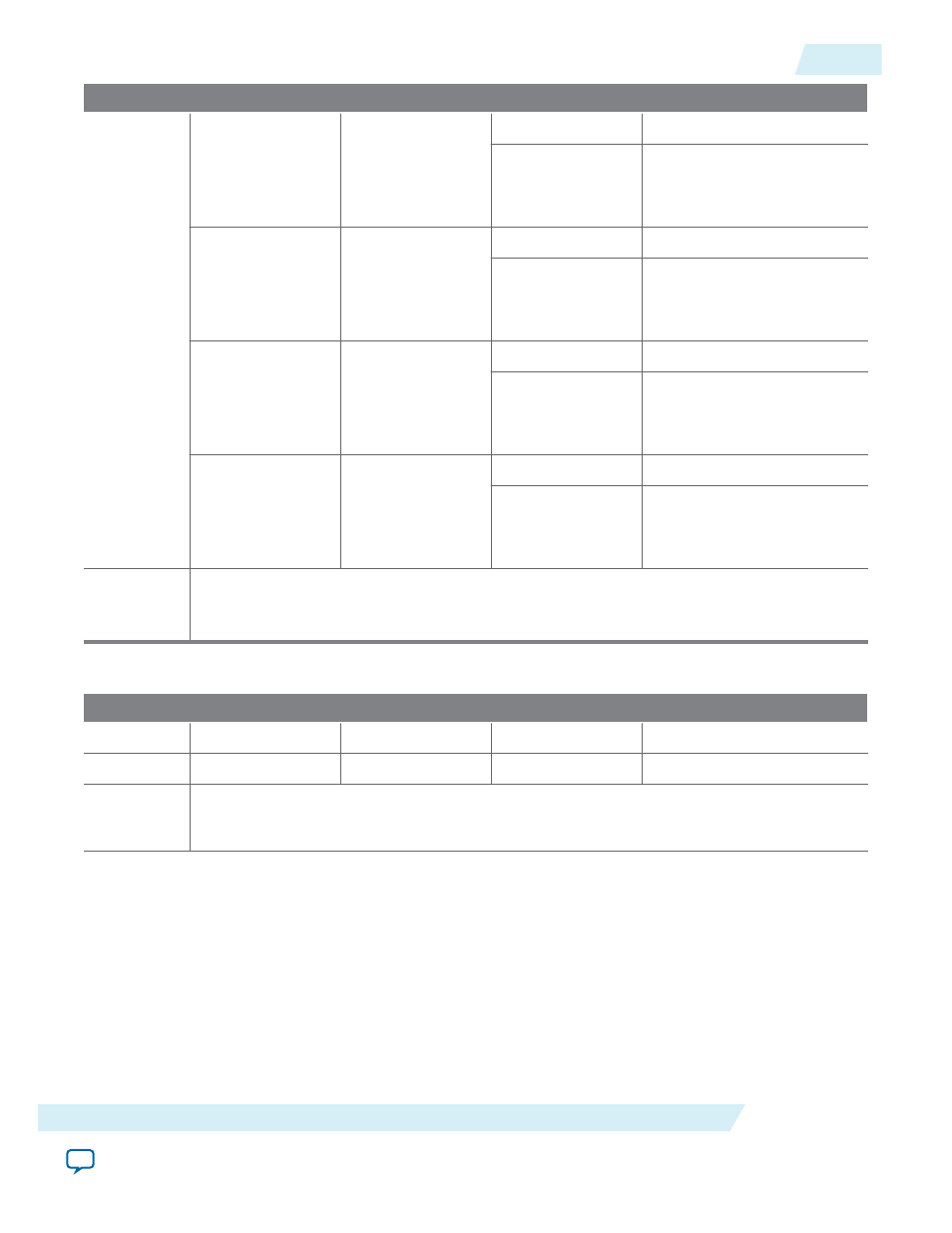

F = 1

F1_

FRAMCL

K_DIV=1

1st frameclk

cnt=0 :

jesd204_rx_

dataout[31:0] =

{F8F12, F0F4}

Case1: M=1, S=2

M0S0=F0F4, M0S1=F8F12

Case2: M=2, S=1

M0S0=F0F4, M1S0=F8F12

2nd frameclk

cnt=1:

jesd204_rx_

dataout[31:0] =

{F9F13, F1F5}

Case1: M=1, S=2

M0S0=F1F5, M0S1=F9F13

Case2: M=2, S=1

M0S0=F1F5, M1S0=F9F13

3rd frameclk

cnt=2:

jesd204_rx_

dataout[31:0] =

{F10F114, F2F6}

Case1: M=1, S=2

M0S0=F2F6, M0S1=F10F14

Case2: M=2, S=1

M0S0=F2F6, M1S0=F10F14

4th frameclk

cnt=3:

jesd204_rx_

dataout[31:0] =

{F11F15, F3F7}

Case1: M=1, S=2

M0S0=F3F7, M0S1=F11F15

Case2: M=2, S=1

M0S0=F3F7, M1S0=F11F15

F1_

FRAMCL

K_DIV=4

jesd204_rx_dataout[127:0] = {{F11F15, F3F7},{F10F114, F2F6},{F9F13, F1F5},{F8F12, F0F4}}

Table 5-14: Data Mapping for F=2, L=4

F = 2

Lane

L3

L2

L1

L0

Data In

{F12, F13, F14, F15} {F8, F9, F10, F11}

{F4, F5, F6, F7}

{F0, F1, F2, F3}

Supported

M and S

M*S=4 for F=2, L=4

F=2 supports either (case1: M=1, S=4), (case2: M=2, S=2) or (case3: M=4, S=1)

UG-01142

2015.05.04

RX Path Data Remapping

5-33

JESD204B IP Core Design Guidelines

Altera Corporation