Registers, Register access type convention, Registers -43 – Altera JESD204B IP User Manual

Page 80: Register access type convention -43

Registers

The JESD204B IP core supports a basic one clock cycle transaction bus. There is no support for burst

mode and wait-state feature (the

avs_waitrequest

signal is tied to 0). The JESD204B IP core Avalon-

MM slave interface has a data width of 32 bits and is implemented based on word addressing. The

Avalon-MM slave interface does not support byte enable access.

Each write transfer has a writeWaitTime of 0 cycle while a read transfer has a readWaitTime of 1 cycle and

readLatency of 1 cycle.

The following HTML files list the TX and RX core registers. The register address in the register map is

written based on byte addressing. The Qsys interconnect automatically converts from byte to word

addressing. You do not need to manually shift the address bus. If the Avalon-MM master interfaces to the

IP core Avalon-MM slave without the Qsys interconnect, to perform byte to word addressing conversion,

you are recommended to shift the Avalon-MM master address bus by 2 bits (divide by 4) when

connecting to the IP core's Avalon-MM slave. In this connection, the Avalon-MM master address bit[2]

connects to the IP core (Avalon-MM slave) address bit[0], while the Avalon-MM master bit[9] connects

to the IP core address bit[7].

•

•

Register Access Type Convention

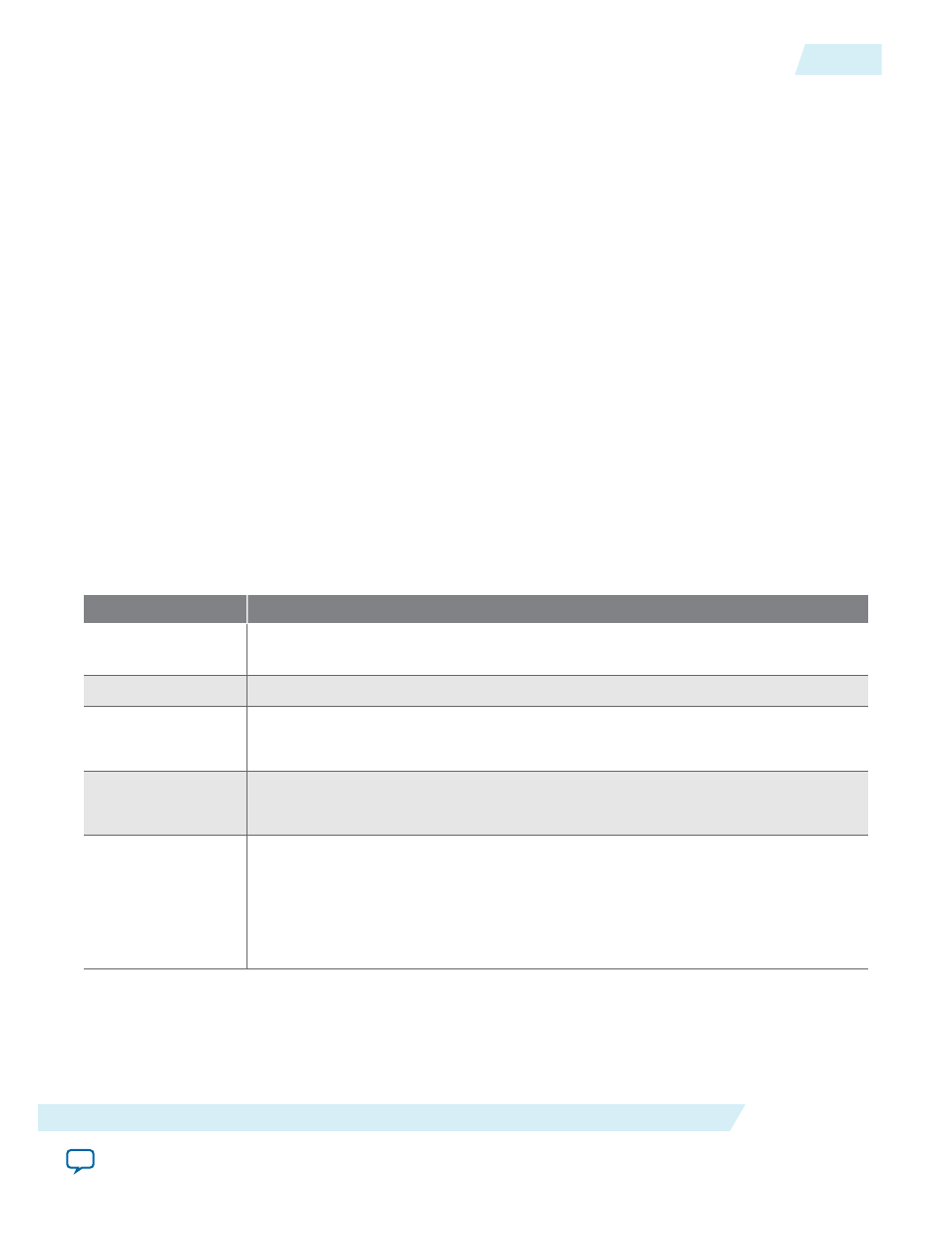

This table describes the register access type for Altera IP cores.

Table 4-7: Register Access Type and Definition

Access Type

Definition

RO

Software read only (no effect on write). The value is hard-tied internally to either '0'

or '1' and does not vary.

RO/v

Software read only (no effect on write). The value may vary.

RC

• Software reads shall return the current bit value, then the bit is self-clear to 0.

• Software reads also cause the bit value to be cleared to 0.

RW

• Software reads shall return the current bit value.

• Software writes shall set the bit to the desired value.

RW1C

• Software reads shall return the current bit value.

• Software writes 0 shall have no effect.

• Software writes 1 shall clear the bit to 0, if the bit has been set to 1 by hardware.

• Hardware sets the bit to 1.

• Software clear has higher priority than hardware set.

UG-01142

2015.05.04

Registers

4-43

JESD204B IP Core Functional Description

Altera Corporation