Rx path operation – Altera JESD204B IP User Manual

Page 111

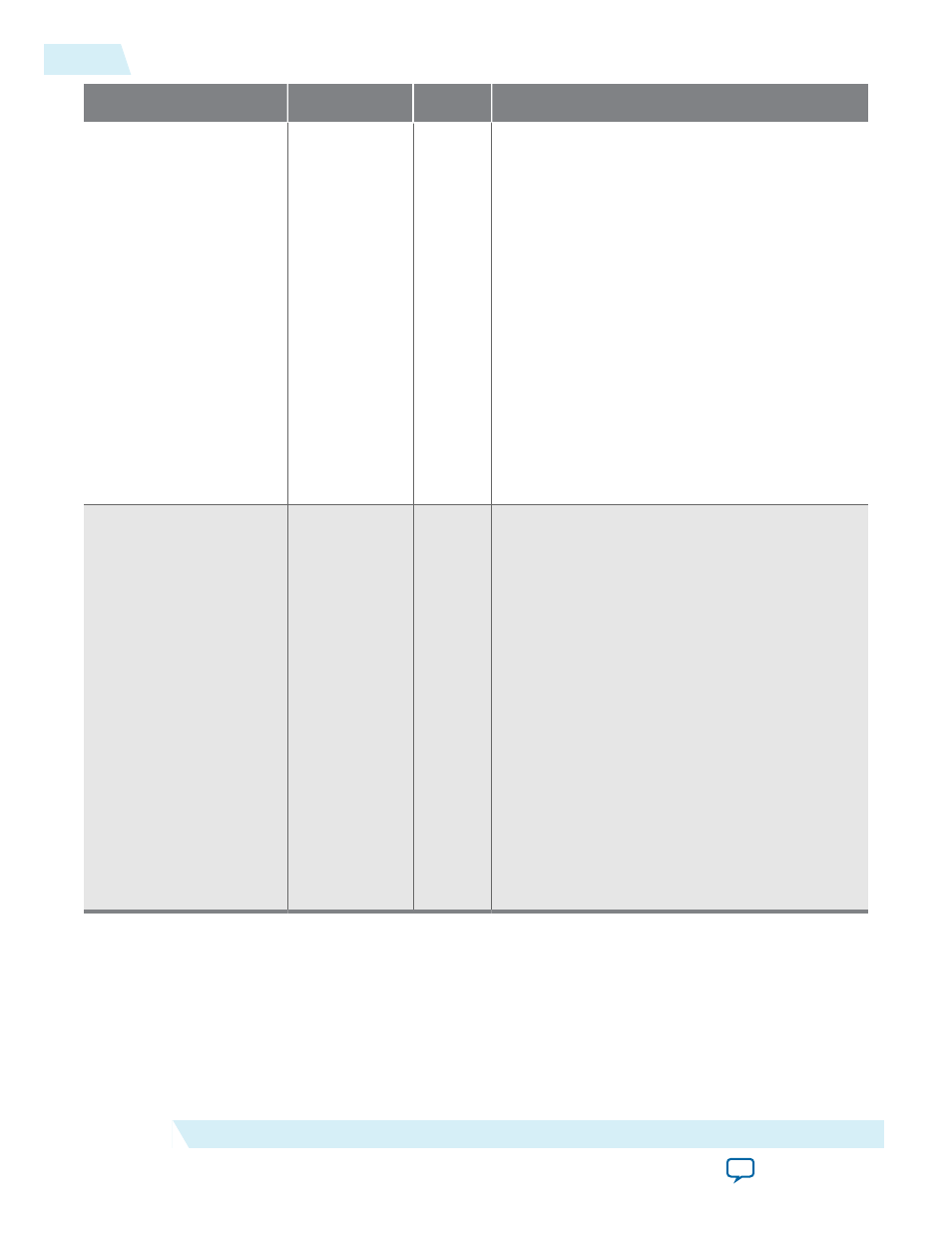

Signal

Clock Domain

Direction

Description

csr_f[7:0]

(35)

mgmt_clk

Input

Indicates the number of octets per frame. This 8-

bit bus represents the F value in zero-based

binary format. For example, if F = 2, the

csr_

f[7:0]

= "00000001". This design example

supports the following values:

• 00000000

• 00000001

• 00000011

• 00000111

Any programmed value beyond the supported

range may result in undeterminable behavior in

the transport layer. You must ensure that the

csr_f[7:0]

value always match the system

parameter F value.

Connect this signal to the RX DLL

csr_f[]

output pin.

csr_n[4:0]

(35)

mgmt_clk

Input

Indicates the converter resolution. This 5-bit bus

represents the N value in zero-based binary

format. For example, if N = 16, the

csr_n[4:0]

=

"01111". This design example supports the

following values:

• 01011

• 01100

• 01101

• 01110

• 01111

Any programmed value beyond the supported

range may result in undeterminable behavior in

the transport layer. You must ensure that the

csr_n[4:0]

value always match the system

parameter N value.

Connect this signal to the RX DLL

csr_n[]

output pin.

RX Path Operation

The data transfer protocol between the Avalon-ST interface and the RX path transport layer is data

transfer without backpressure. Therefore, the sink shall always be ready to sample the incoming data

whenever data at the source is valid.

5-30

RX Path Operation

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Design Guidelines