Altera JESD204B IP User Manual

Page 74

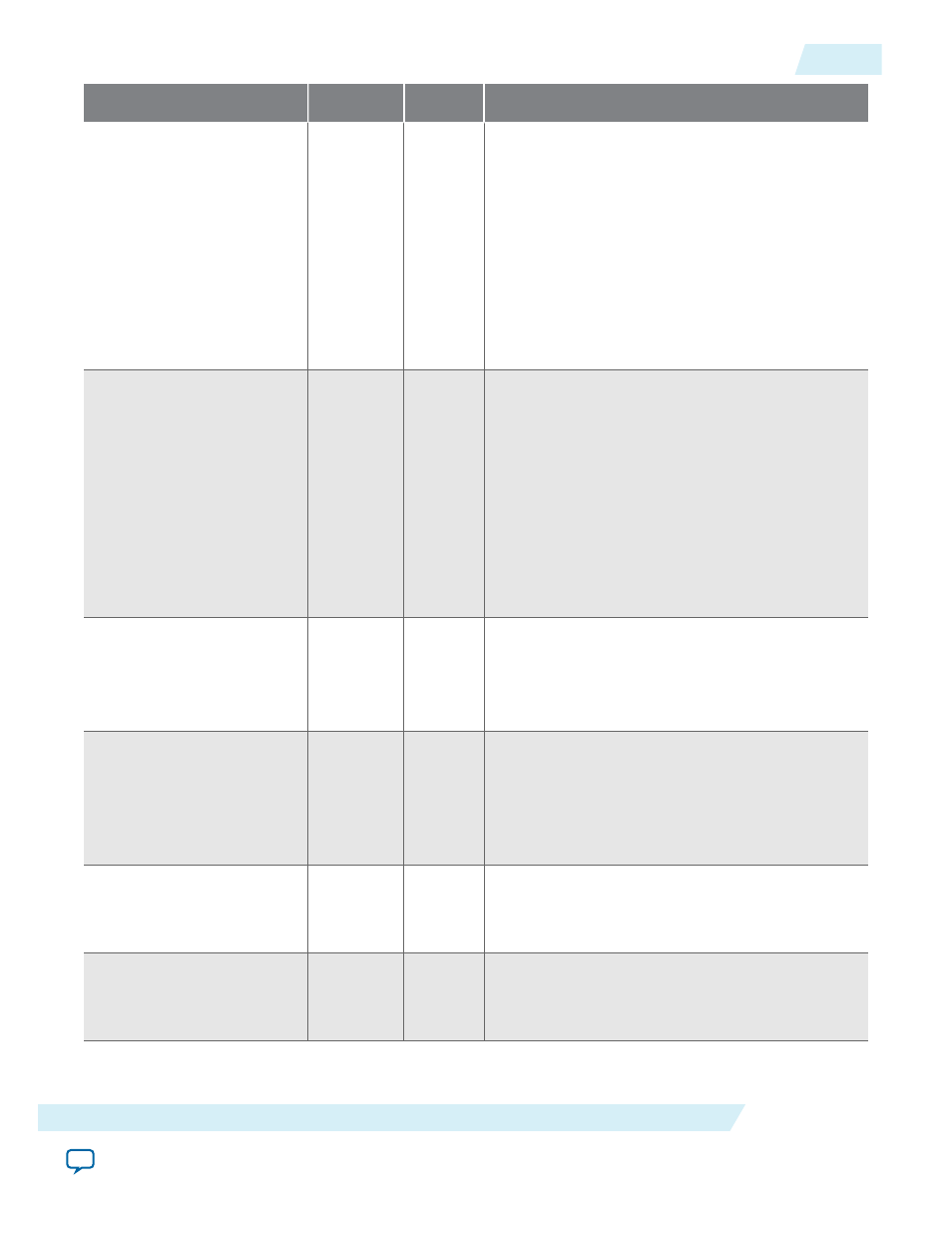

Signal

Width

Direction

Description

reconfig_to_xcvr[]

L*70

Input

Dynamic reconfiguration input for the hard

transceiver.

This signal is only applicable for V series FPGA

variants.

You must connect these signals to the Transceiver

Reconfiguration Controller IP core regardless of

whether run-time reconfiguration is enabled or

disabled. The Transceiver Reconfiguration

Controller IP core also supports various calibra‐

tion function during transceiver power up.

reconfig_from_xcvr[]

L*46

Output

Dynamic reconfiguration output for the hard

transceiver.

This signal is only applicable for V series FPGA

variants.

You must connect these signals to the Transceiver

Reconfiguration Controller IP core regardless of

whether run-time reconfiguration is enabled or

disabled. The Transceiver Reconfiguration

Controller IP core also supports various calibra‐

tion function during transceiver power up.

reconfig_clk

1

Input

The Avalon-MM clock input. The frequency range

is 100–125 MHz.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

reconfig_reset

1

Input

Reset signal for the Transceiver Reconfiguration

Controller IP core. This signal is active high and

level sensitive.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

reconfig_avmm_

address[]

log

2

L*1024 Input

The Avalon-MM address.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

reconfig_avmm_

writedata[]

32

Input

The input data.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

UG-01142

2015.05.04

Receiver

4-37

JESD204B IP Core Functional Description

Altera Corporation