Rx phy layer, Rx phy layer -12 – Altera JESD204B IP User Manual

Page 49

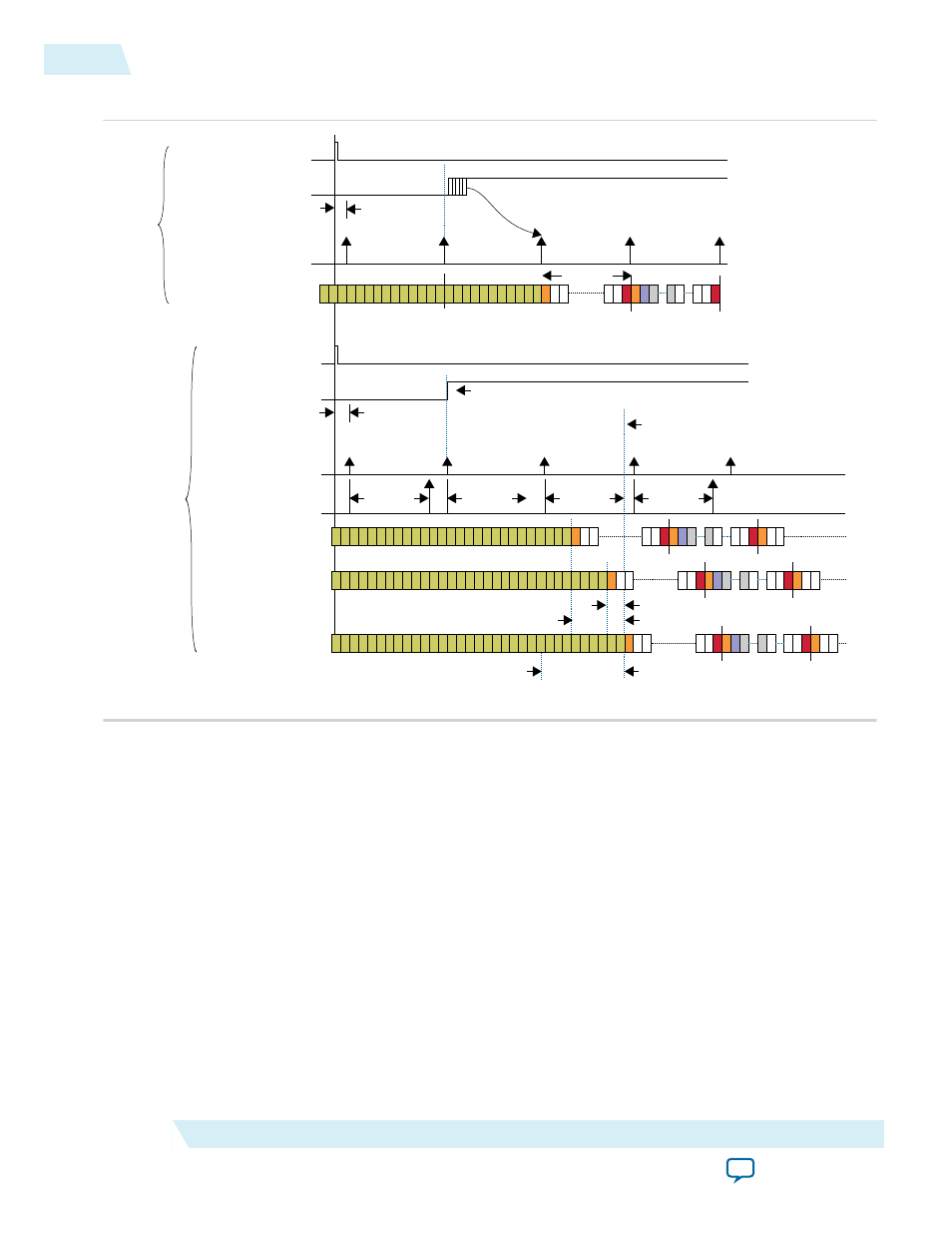

Figure 4-5: Subclass 1 Deterministic Latency and Support for Programmable Release Opportunity

K K K K K K K K K K K K K K K K K K K K K K K K K KR D D

D D A R Q C C D D D A

L Transmit Lanes

SYSREF

SYNC_N

LMFC

Deterministic Delay from SYSREF

Sampled High to LMFC Zero-Crossing

TX ILA Begins on First LMFC Zero-Crossing

after SYNC_N Is Deasserted

Multi-Frame

TX

Device

K K K K K K K K K K K K

K

R D D

D D A R Q C C D D D A R D D

Earliest Arrival Lane

SYSREF

SYNC_N

LMFC

Deterministic Delay from

SYSREF Sampled High

to LMFC Zero-Crossing

RX Elastic Buffers Released

RX

Device

K K

K K K K K K K K

K K K K K

R D D

D D A R Q C C D D D A R D D

K K

K K K K K K

K K K K K K K

R D D

D D A R Q C C D D D A R D D

K K

K K K K

K K K K K K K K

K K K K

K K K K K K K K

K K K K

K K

K K K K

K K K K K K K

K K

K K K

Latest Arrival Lane

Aligned Output on All Lanes

RX Elastic Buffer

Release Opportunity

RBD Frame

Cycles

SYNC_N Deasserted Directly after LMFC Zero Crossing

RBD Frame

Cycles

RBD Frame

Cycles

RBD Frame

Cycles

2 Character Elastic Buffer Delay for Latest Arrival

6 Character Elastic Buffer Delay for Latest Arrival

Deterministic Delay

from TX ILA Output

to RX ILA Output

RX PHY Layer

The word aligner block identifies the MSB and LSB boundaries of the 10-bit character from the serial bit

stream. Manual alignment is set because the /K/ character must be detected in either LSB first or MSB first

mode. When the programmed word alignment pattern is detected in the current word boundary, the PCS

indicates a valid pattern in the

rx_sync_status

(mapped as

pcs_valid

to the IP core). The code

synchronization state is detected after the detection of the /K/ character boundary for all lanes.

In a normal operation, whenever synchronization is lost, JESD204 RX IP core always return back to the

CS_INIT

state where the word alignment is initiated. For debug purposes, you can bypass this alignment

by setting the

csr_patternalign_en

register to 0.

The 8B/10B decoder decode the data after receiving the data through the serial line. The JESD204 IP core

supports transmission order from MSB first as well as LSB first.

The PHY layer can detect 8B/10B not-in-table (NIT) error and also running disparity error.

4-12

RX PHY Layer

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description