Altera JESD204B IP User Manual

Page 79

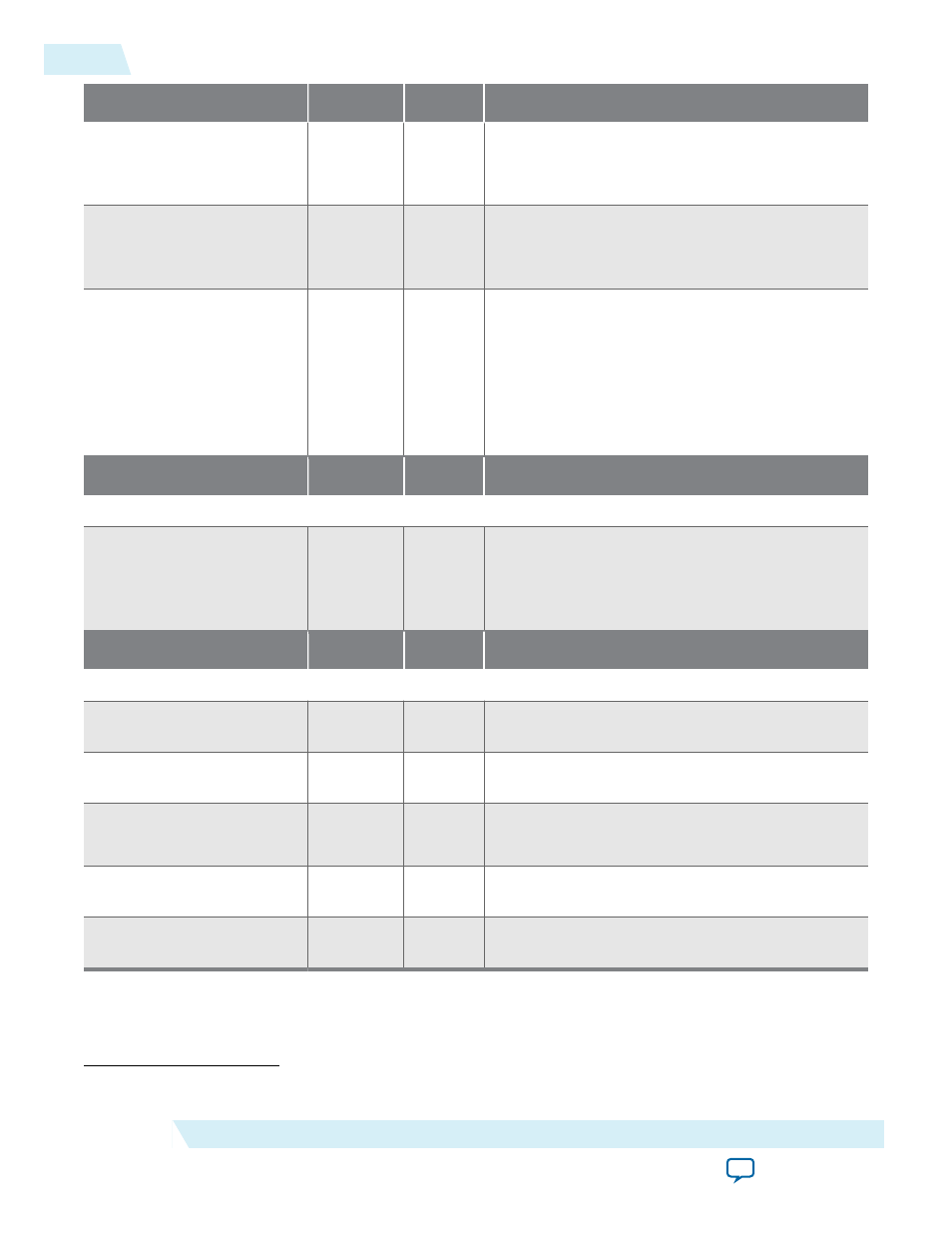

Signal

Width

Direction

Description

csr_cf[]

5

Output

Indicates the number of control words per frame

clock period per link. The transport layer can use

this signal as a run-time parameter.

csr_lane_powerdown[]

L

Output

Indicates which lane is powered down. You need

to set this signal if you have configured the link

and want to reduce the number of active lanes.

csr_rx_testmode[]

4

Output

Indicates the address space that is reserved for DLL

testing within the JESD204B IP core.

• 0—reserved for the IP core.

• 1—program different tests in the transport

layer.

Refer to the

csr_rx_testmode

register.

Signal

Width

Direction

Description

Out-of-band (OOB)

jesd204_rx_int

1

Output

Interrupt pin for the JESD204B IP core. Interrupt

is asserted when any error is detected. Configure

the

rx_err_enable

register to set the type of error

that can trigger an interrupt.

Signal

Width

Direction

Description

Debug or Testing

jesd204_rx_dlb_data[]

L*32

Input

Optional signal for parallel data to the DLL in TX

to RX loopback testing.

(26)

jesd204_rx_dlb_data_

valid[]

L

Input

Optional signal to indicate valid data for each byte

in TX to RX loopback testing.

(26)

jesd204_rx_dlb_kchar_

data[]

L*4

Input

Optional signal to indicate the K character value

for each byte in TX to RX loopback testing.

(26)

jesd204_rx_dlb_

errdetect[]

L*4

Input

Optional signal to indicate 8B/10B error.

(26)

jesd204_rx_dlb_

disperr[]

L*4

Input

Optional signal to indicate running disparity.

(26)

(26)

This signal is only for internal testing purposes. Tie this signal to low.

4-42

Receiver

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description