Jesd204b ip core parameters, Jesd204b ip core parameters -16 – Altera JESD204B IP User Manual

Page 30

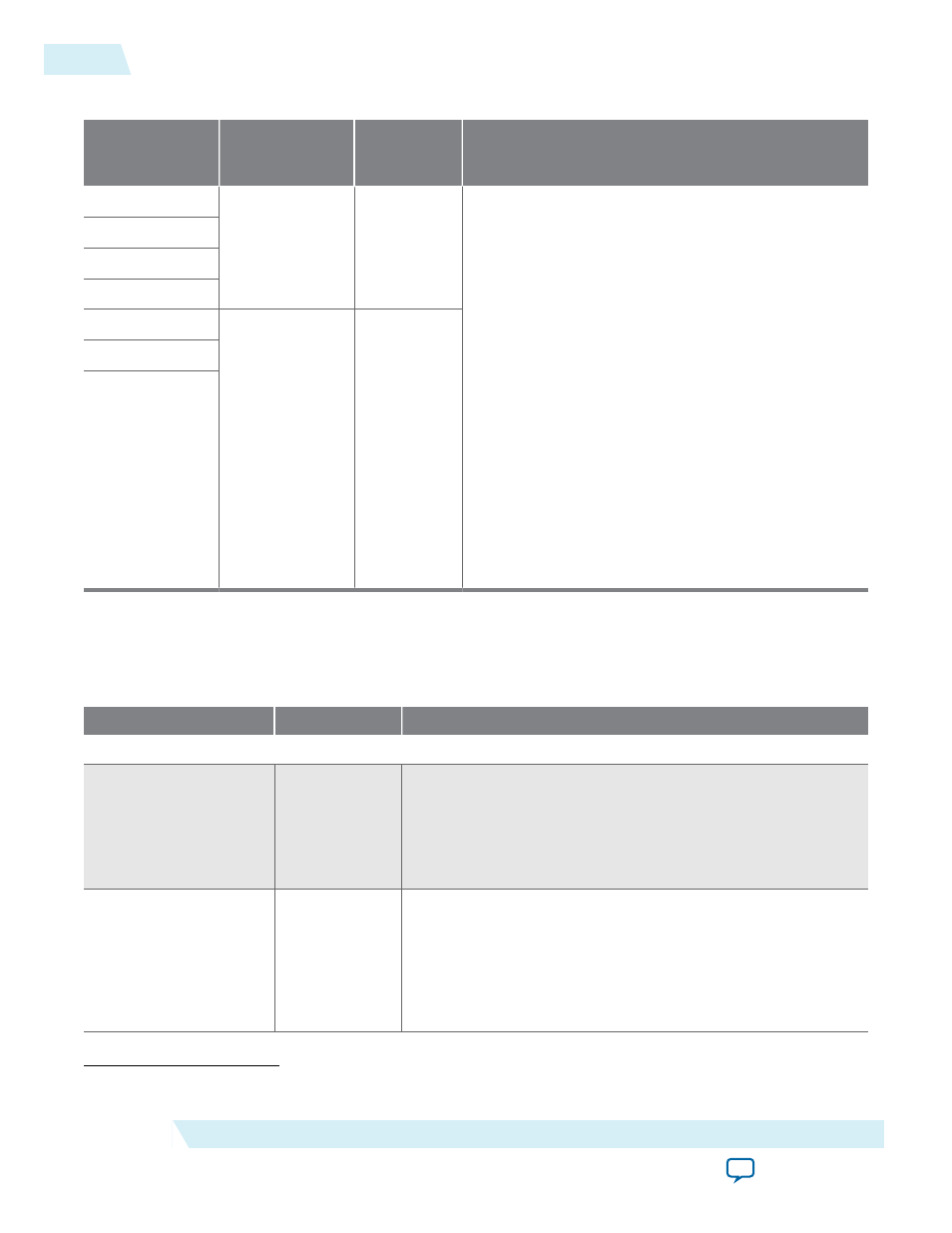

Table 3-5: Example B

Original clock

names in altera_

jesd204.sdc

User design input

clock names

Frequency

(MHz)

Recommended SDC timing constraint

tx_pll_ref_clk

device_clk

125

create_clock -name device_clk -period 8.0 [get_ports

device_clk]

create_clock -name mgmt_clk -period 10.0 [get_ports

mgmt_clk]

derive_pll_clocks

set_clock_groups -asynchronous \

-group {device_clk \

<base and generated clock names as reported by

report_clock commands> \

} \

-group {mgmt_clk \

<base and generated clock names as reported by

report_clock commands> \

}

rx_pll_ref_clk

txlink_clk

rxlink_clk

tx_avs_clk

mgmt_clk

100

rx_avs_clk

reconfig_clk

(11)

JESD204B IP Core Parameters

Table 3-6: JESD204B IP Core Parameters

Parameter

Value

Description

Main Tab

Device Family

• Arria V

• Arria V GZ

• Arria 10

• Cyclone V

• Stratix V

Select the targeted device family.

JESD204B Wrapper

• Base Only

• PHY Only

• Both Base

and PHY

Select the JESD204B wrapper.

• Base Only—generates the DLL only.

• PHY Only—generates the transceiver PHY layer only (soft

and hard PCS).

• Both Base and PHY—generates both DLL and transceiver

PHY layers.

(11)

For Arria 10 device only.

3-16

JESD204B IP Core Parameters

UG-01142

2015.05.04

Altera Corporation

Getting Started