Tx path data remapping, Tx path, Data remapping – Altera JESD204B IP User Manual

Page 99: Section

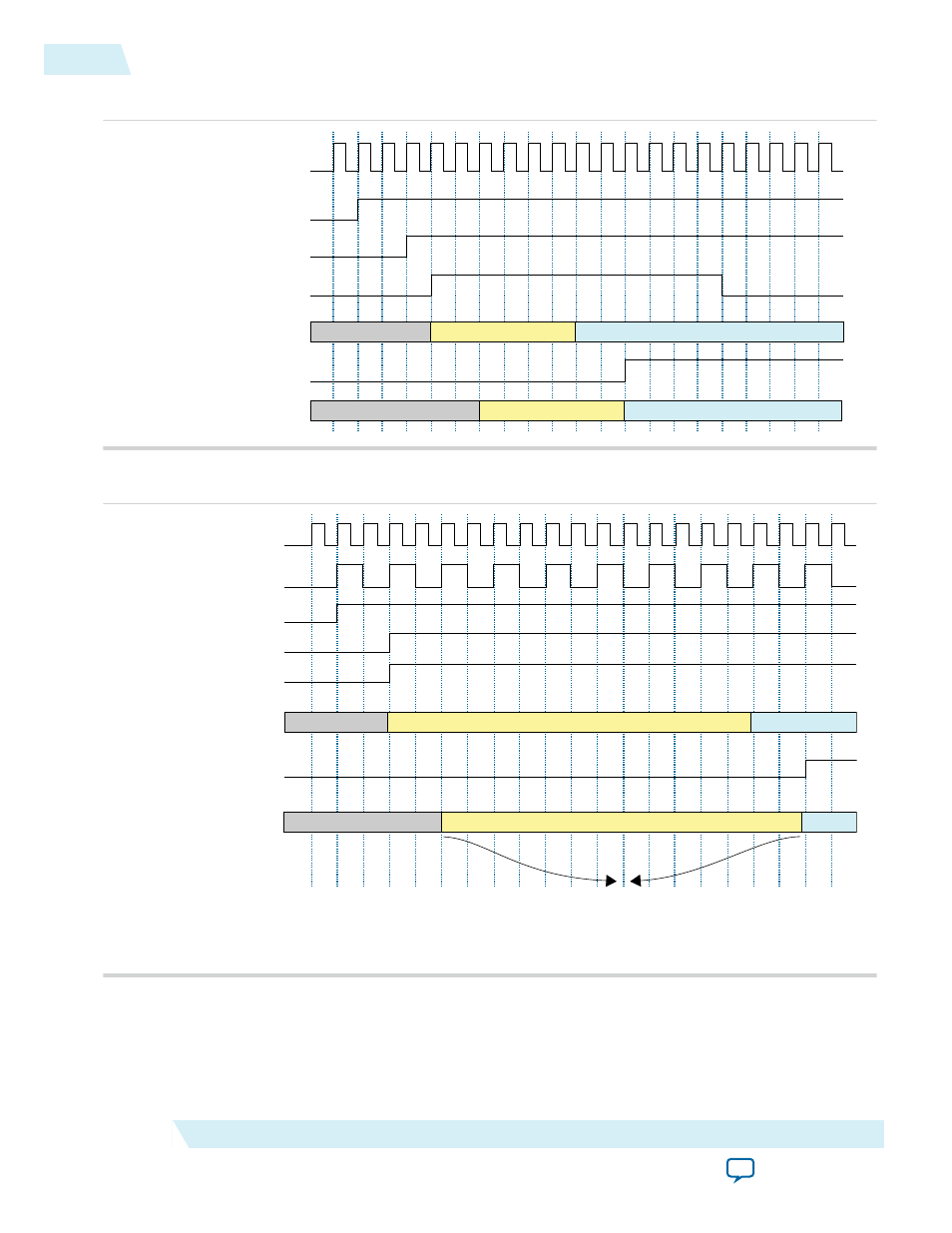

Figure 5-5: TX Data Transmission

Junk

datain

Valid Data

Junk

Sampled Data

Valid Data

txframe_clk

txlink_clk

txframe_rst_n

txlink_rst_n

jesd204_tx_datavalid

TL.jesd204_tx_link_early_ready

jesd204_tx_datain[15:0]

LINK.jesd204_tx_link_ready

jesd204_tx_link_datain[31:0]

Figure 5-6: TX Data Transmission (For F = 8)

Junk

datain

Valid Data

Junk

Sampled Data

Valid Data

txlink_clk

txframe_rst_n

txlink_rst_n

jesd204_tx_datavalid

jesd204_tx_link_early_ready

jesd204_tx_datain[63:0]

LINK.jesd204_tx_link_ready

jesd204_tx_link_datain[31:0]

txframe_clk

T0 -->T1

When F = 8, the data latency for jesd204_tx_link_datain should always

be in an even latency link_clk count to ensure that the first valid data captured

by the TX link is T0 data followed by T1 data.

TX Path Data Remapping

The JESD204B IP core implements the data transfer in big endian format.

5-18

TX Path Data Remapping

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Design Guidelines