Operation, Operating modes, Operation -13 – Altera JESD204B IP User Manual

Page 50: Operating modes -13

Operation

Operating Modes

The JESD204B IP core supports Subclass 0, 1, and 2 operating modes.

Subclass 0

The JESD204 IP core maintains a LMFC counter that counts from 0 to (F × K/4)–1 and wraps around

again. The LMFC counter starts counting at the deassertion of SYNC_N signal from multiple DACs after

synchronization. This is to align the LMFC counter upon transmission and can only be done after all the

converter devices have deasserted its synchronization request signal.

Subclass 1

The JESD204 IP core maintains a LMFC counter that counts from 0 to (F × K/4)–1 and wraps around

again. The LMFC counter will reset within two link clock cycles after converter devices issue a common

SYSREF frequency to all the transmitters and receivers. The SYSREF frequency must be the same for

converter devices that are grouped and synchronized together.

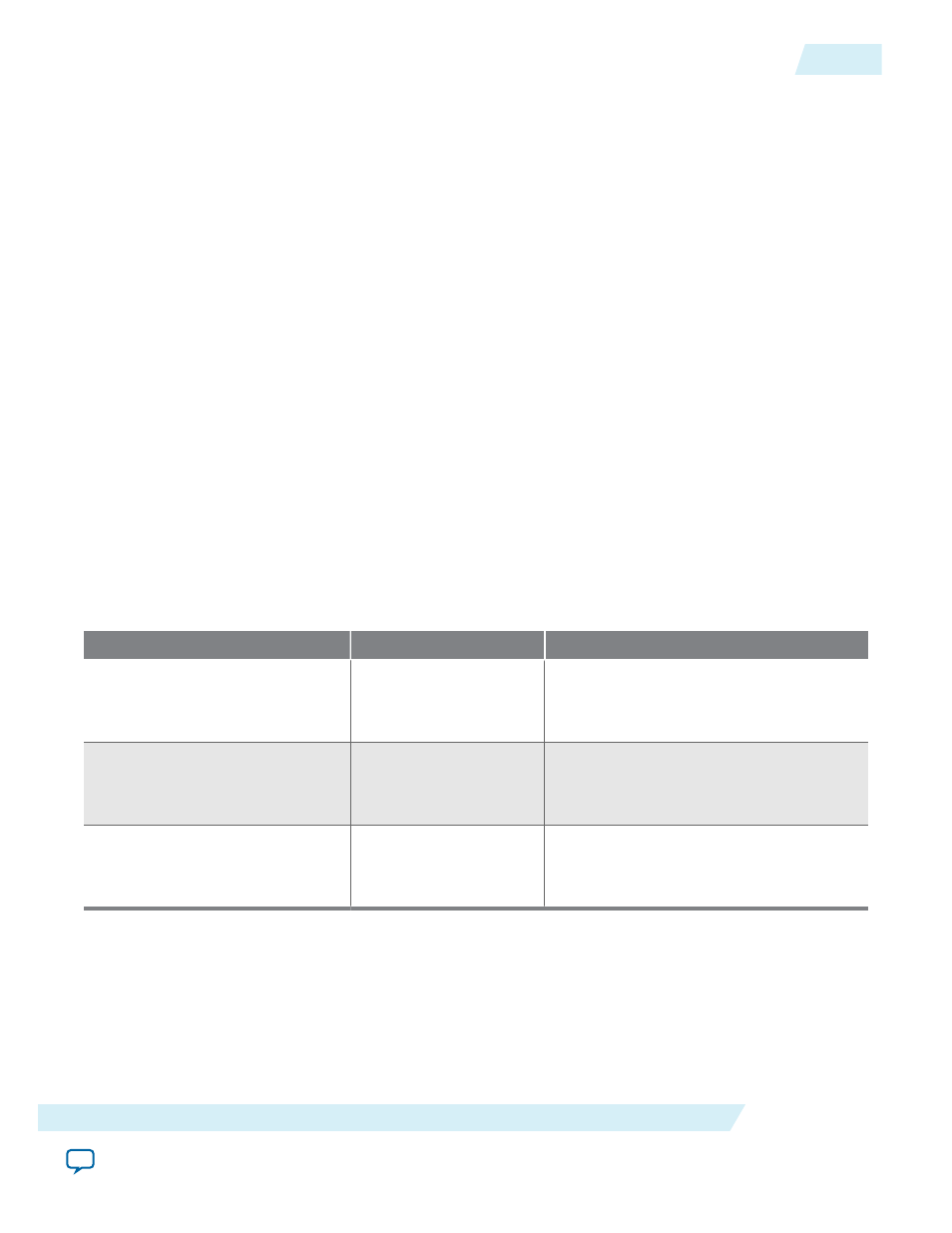

Table 4-2: Example of SYSREF Frequency Calculation

In this example, you can choose to perform one of the following options:

• provide two SYSREF and device clock, where the ADC groups share both the device clock and SYSREF (18.75

MHz and 9.375 MHz)

• provide one SYSREF (running at 9.375 MHz) and device clock for all the ADC and DAC groups because the

SYSREF period in the DAC is a multiplication of n integer.

Group

Configuration

SYSREF Frequency

ADC Group 1 (2 ADCs)

• LMF = 222

• K = 16

• Data rate = 6 Gbps

(6 GHz / 40) / (2 x 16 / 4) = 18.75 MHz

ADC Group 2 (2 ADCs)

• LMF = 811

• K = 32

• Data rate = 6 Gbps

(6 GHz / 40) / (1 x 32 / 4) = 18.75 MHz

DAC Group 3 (2 DACs)

• LMF = 222

• K = 16

• Data rate = 3 Gbps

(3 GHz / 40) / (2 x 16 / 4) = 9.375 MHz

Subclass 2

The JESD204 IP core maintains a LMFC counter that counts from 0 to (F × K/4)–1 and wraps around

again. The LMFC count starts upon reset and the logic device always acts as the timing master. The

converters adjust their own internal LMFC to match the master's counter. The alignment of LMFC within

the system relies on the correct alignment of SYNC_N signal deassertion at the LMFC boundary.

The alignment of LMFC to RX logic is handled within the TX converter. The RX logic releases SYNC_N at

the LMFC tick and the TX converter adjust its internal LMFC to match the RX LMFC.

UG-01142

2015.05.04

Operation

4-13

JESD204B IP Core Functional Description

Altera Corporation