Altera JESD204B IP User Manual

Page 70

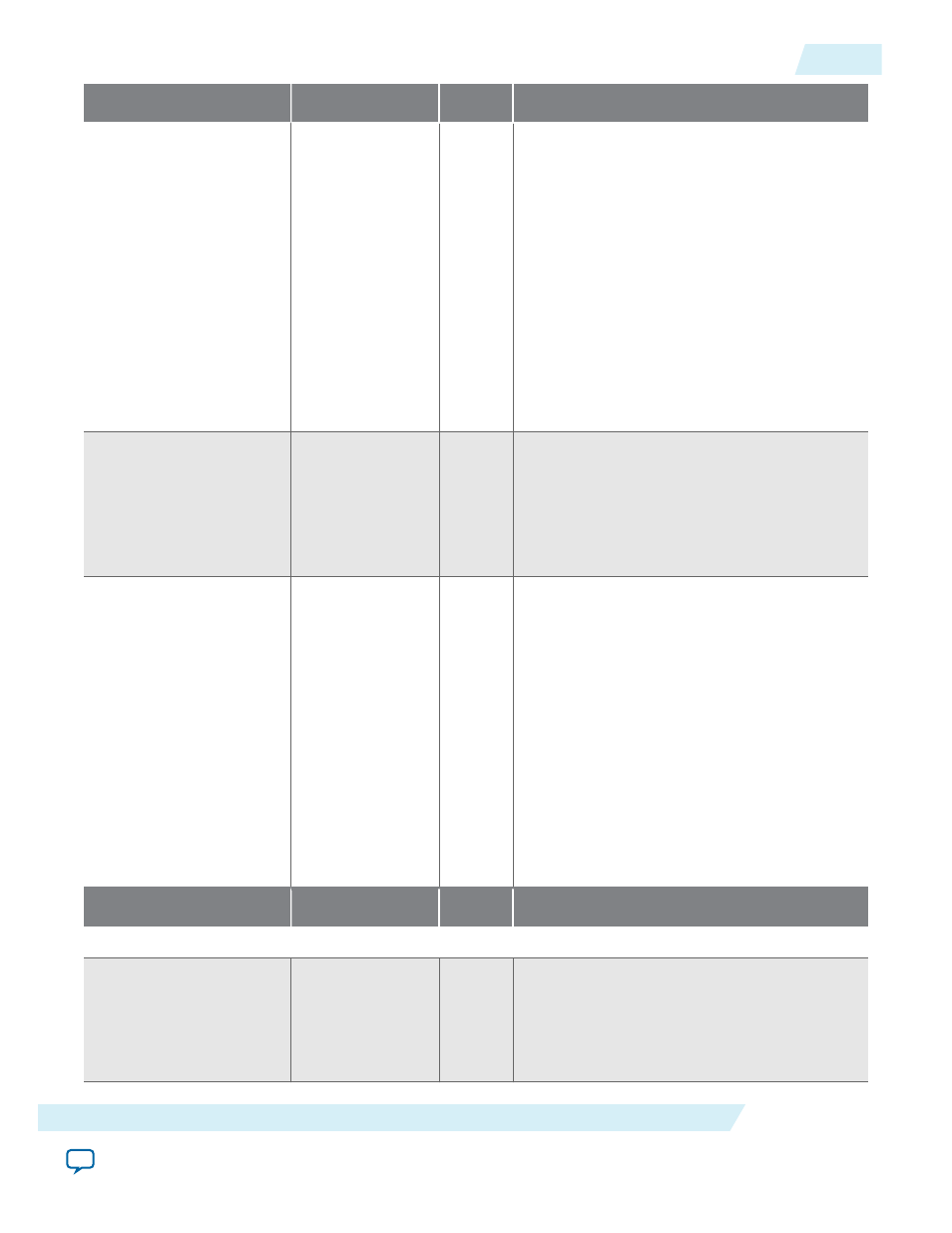

Signal

Width

Direction

Description

sync_n

1

Input

Indicates

SYNC_N

from the converter device or

receiver. This is an active low signal and is

asserted 0 to indicate a synchronization

request or error reporting from the converter

device.

To indicate a synchronization request, the

converter device must assert this signal for at

least five frames and nine octets.

To indicate an error reporting, the converter

device must ensure that the pulse is at least

one cycle of the

txlink_clk

signal or two

cycles of the

txframe_clk

signal (whichever

period is longer).

dev_sync_n

1

Output

Indicates a clean synchronization request. This

is an active low signal and is asserted 0 to

indicate a synchronization request only. The

sync_n

signal error reporting is being masked

out of this signal. This signal is also asserted

during software-initiated synchronization.

mdev_sync_n

1

Input

Indicates a multidevice synchronization

request. Synchronize signal combination

should be done externally and then input to

the JESD204B IP core through this signal.

• For subclass 0—combine the

dev_sync_n

signal from all multipoint links before

connecting to the

mdev_sync_n

signal.

• For subclass 1—connect the

dev_sync_n

signal to the

mdev_sync_n

signal for each

link respectively.

In a single link instance where multidevice

synchronization is not needed, tie the

dev_

sync_n

signal to this signal.

Signal

Width

Direction

Description

CSR

jesd204_tx_frame_

error

1

Input

Optional signal to indicate an empty data

stream due to invalid data. This signal is

asserted high to indicate an error during data

transfer from the transport layer to the TX

core.

UG-01142

2015.05.04

Transmitter

4-33

JESD204B IP Core Functional Description

Altera Corporation