Tx data transmission – Altera JESD204B IP User Manual

Page 98

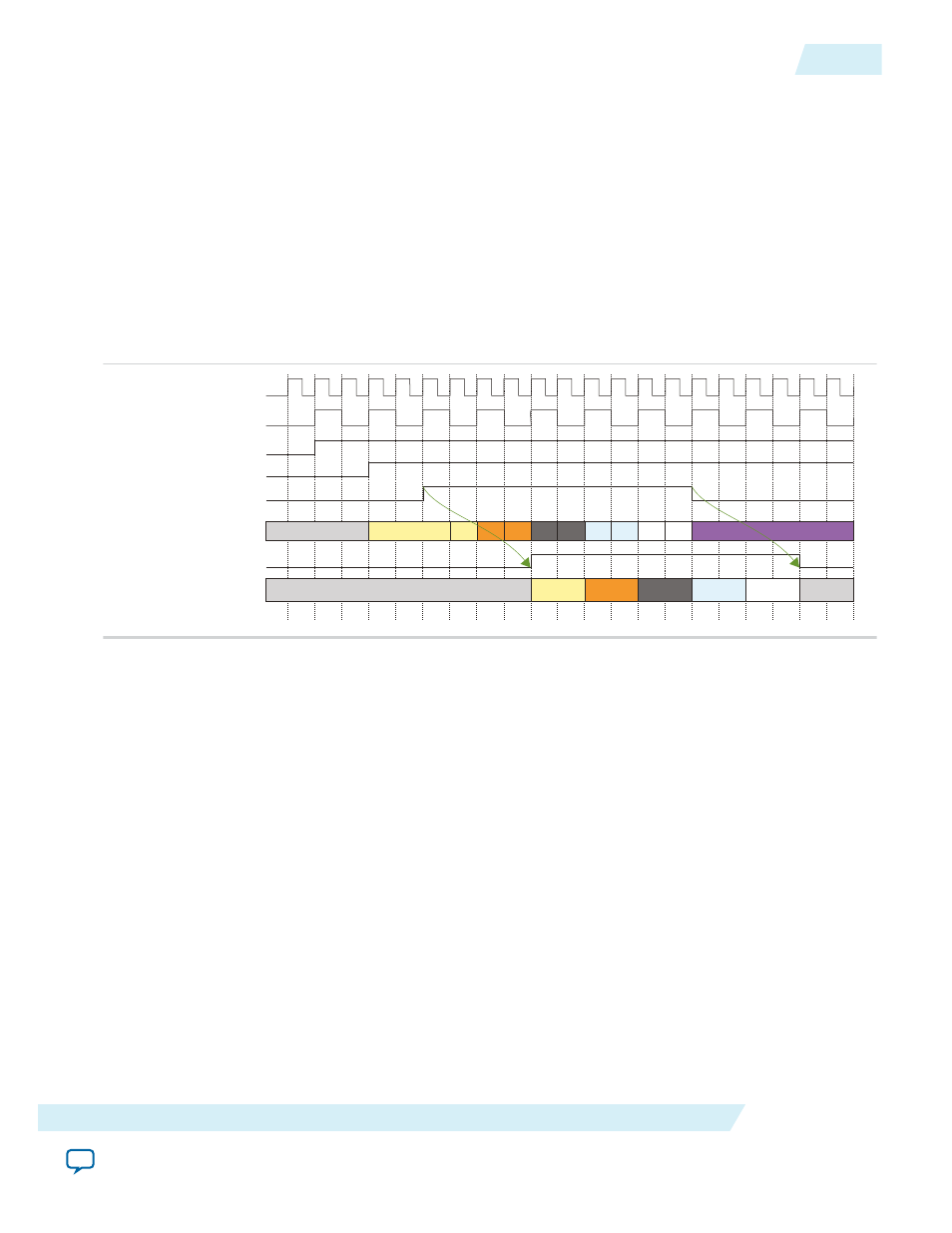

Figure 5-4: TX Operation Behavior

This figure shows the data transmission for a system configuration of LMF = 112, N = N' = 16, S = 1.

Operation:

• Upon the deassertion of the

txframe_rst_n

signal, the

jesd204_tx_link_early_ready

signal from

the DLL to the transport layer is asserted some time later, which activates the transport layer to start

sampling the

jesd204_tx_datain[15:0]

signal from the Avalon-ST interface.

• Each sampled 16-bit data is first written in a FIFO with a depth of four.

• Once the FIFO accumulates 32-bit data, the data is streamed to the DLL accordingly through the

jesd204_tx_link_datain[31:0]

signal.

• Finally, the

jesd204_tx_link_early_ready

and

jesd204_tx_data_ready

signals deassert because

the DLL has entered code group synchronization state in this scenario.

txframe_clk

txlink_clk

txframe_rst_n/txlink_rst_n

jesd204_tx_data_valid

jesd204_tx_link_early_ready/

jesd204_tx_data_ready

jesd204_tx_datain[15:0]

jesd204_tx_link_data_valid

jesd204_tx_link_datain[31:0]

junk

All 0s

d0[15:0]

d1[15:0] d2[15:0] d3[15:0]

d4[15:0] d5[15:0]

d6[15:0] d7[15:0] d8[15:0] d9[15:0] d10[15:0]

d0[15:0]

d1[15:0]

d2[15:0]

d3[15:0]

d4[15:0]

d5[15:0]

d6[15:0]

d7[15:0]

d8[15:0]

d9[15:0]

All 0s

TX Data Transmission

This section explains the data transmission behavior when there is a valid TX data out from the TL to

DLL.

Upon the deassertion of

txframe_rst_n

signal, the link's

jesd204_tx_link_early_ready

signal equals

to "1". This setting activates the TL to start sampling

jesd204_tx_datain

signal from the Avalon-ST

interface and transmits sampled data (

jesd204_tx_link_datain

) to the TX link. The TX link only

captures valid data from the TL when the

jesd204_tx_link_ready

signal equals to "1" (in user data

phase). This means all the data transmitted from the TL before

jesd204_tx_link_ready

signal equals to

"1" are ignored.

UG-01142

2015.05.04

TX Data Transmission

5-17

JESD204B IP Core Design Guidelines

Altera Corporation