Error reporting through sync_n signal, Clocking scheme, Error reporting through sync_n signal -18 – Altera JESD204B IP User Manual

Page 55: Clocking scheme -18

RX (Subclass 0)

The JESD204B RX IP core drives and holds

SYNC_N

(

dev_sync_n

signal) low when it is in reset. Upon

reset deassertion, the JESD204B RX IP core checks if there is sufficient /K/ character to move its state

machine out of synchronization request. Once sufficient /K/ character is detected, the IP core deasserts

SYNC_N

.

RX (Subclass 1)

The JESD204B RX IP core drives and holds the

SYNC_N

(

dev_sync_n

signal) low when it is in reset. Upon

reset deassertion, the JESD204B RX IP core checks if there is sufficient /K/ character to move its state

machine out of synchronization request. The IP core also ensures that at least one SYSREF rising edge is

sampled before deasserting

SYNC_N

. This is to prevent a race condition where the

SYNC_N

is deasserted

based on internal free-running LMFC count instead of the updated LMFC count after SYSREF is sampled.

RX (Subclass 2)

The JESD204B RX IP core behaves the same as in Subclass 1 mode. In this mode, the logic device is always

the master timing reference. Upon

SYNC_N

deassertion, the ADC adjusts the LMFC timing to match the IP

core.

Error Reporting Through SYNC_N Signal

The JESD204 TX IP core can detect error reporting through

SYNC_N

when

SYNC_N

is asserted for two

frame clock periods (if F >= 2) or four frame clock periods (if F = 1). When the downstream device

reports an error through

SYNC_N

, the TX IP core issues an interrupt. The TX IP core samples the

SYNC_N

pulse width using the link clock.

For a special case of F = 1, two frame clock periods are less than one link clock. Therefore, the error

signaling from the receiver may be lost. You must program the converter device to extend the

SYNC_N

pulse to four frame clocks when F = 1.

The JESD204 RX IP core does not report an error through

SYNC_N

signaling. Instead, the RX IP core

issues an interrupt when any error is detected.

You can check the

csr_tx_err

,

csr_rx_err0

, and

csr_rx_err1

register status to determine the error

types.

Clocking Scheme

This section describes the clocking scheme for the JESD204B IP core and transceiver.

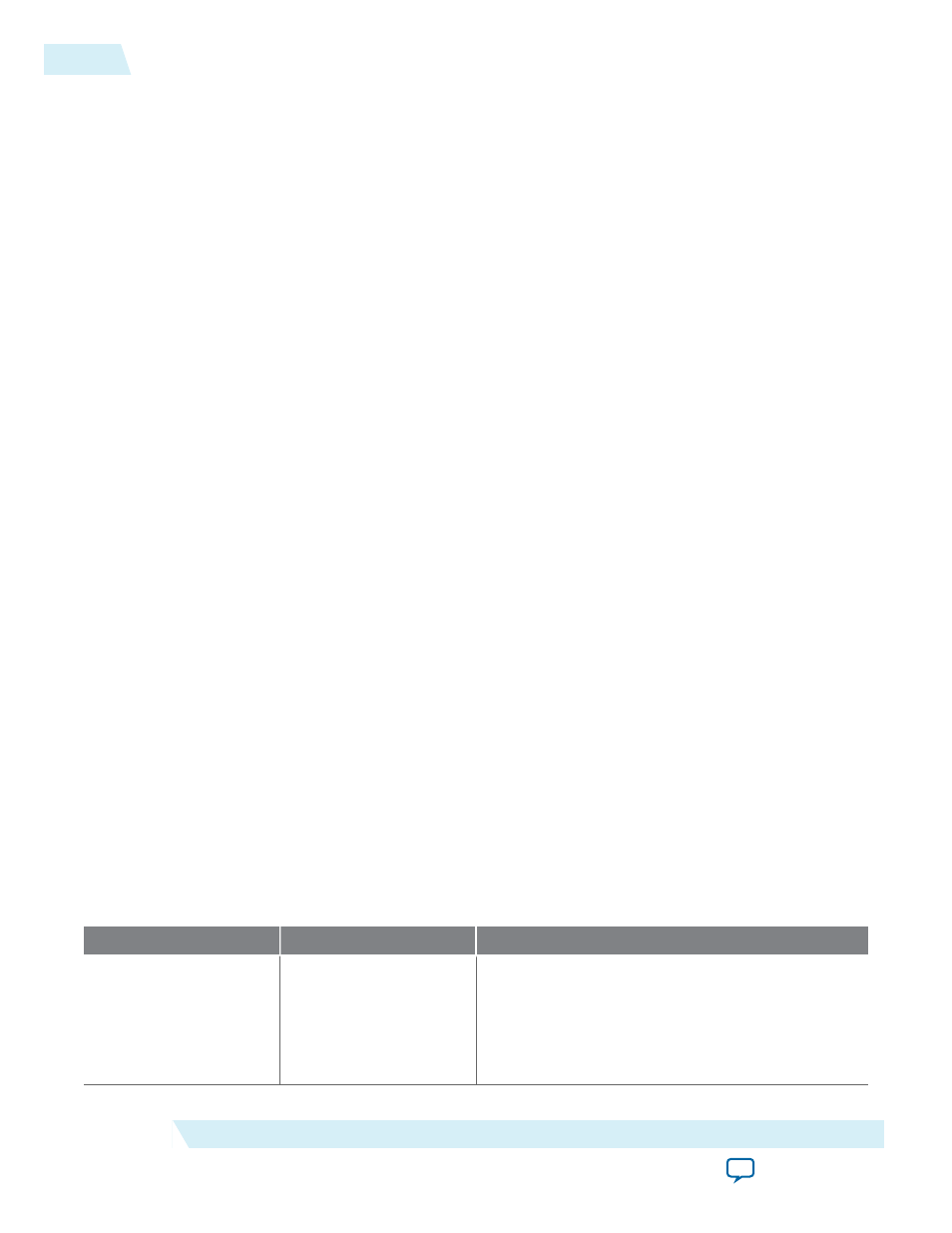

Table 4-3: JESD204B IP Core Clocks

Clock Signal

Formula

Description

TX/RX Device Clock:

pll_ref_clk

PLL selection during IP

core generation

The PLL reference clock used by the TX Transceiver

PLL or RX CDR.

This is also the recommended reference clock to the

Altera PLL IP Core (for Arria V or Stratix V

devices) or Altera IOPLL (for Arria10 devices).

4-18

Error Reporting Through SYNC_N Signal

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description