Altera JESD204B IP User Manual

Page 40

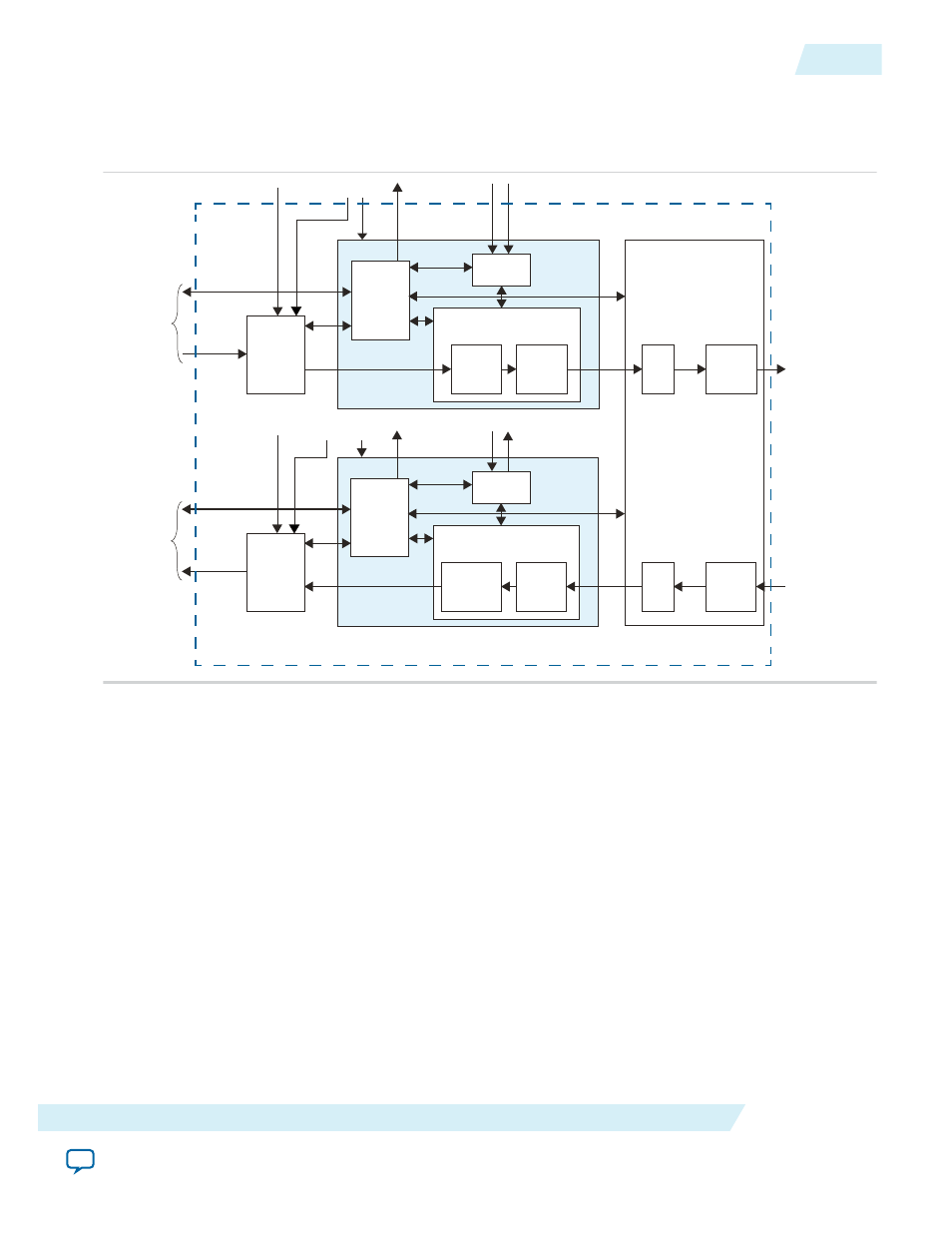

Figure 4-2: JESD204B IP Core TX and RX Datapath Block Diagram

The JESD204B IP core utilizes the Avalon-ST source and sink interfaces, with unidirectional flow of data,

to transmit and receive data on the FPGA fabric interface.

TX Frame

Assembly

Per Device

TX CSR

Per Device

TX CTL

Per Device

Scrambler

Data Link

Layer (TX)

Soft

PCS

(TX)

Hard PCS

and

Transceiver

JESD204B

(TX) Per Device

CSR

CSR

CSR

32 Bit PCS

Per Channel

Transceiver (Duplex)

Per Device

SYNC_N

SYSREF

TX_INT

TXLINK_CLK

TXFRAME_CLK

Avalon-MM

Avalon-ST

To Avalon

Interface

Bus

RX Frame

Deassembly

Per Device

RX CSR

Per Device

RX CTL

Per Device

Descrambler

Data Link

Layer (RX)

Soft

PCS

(RX)

Hard PCS

and

Transceiver

JESD204B

(RX) Per Device

CSR

CSR

CSR

CSR

CSR

32 Bit PCS

Per Channel

32/40

PCS

SYNC_N

SYSREF

RX_INT

RXLINK_CLK

RXFRAME_CLK

Avalon-MM

Avalon-ST

To Avalon

Interface

Bus

JESD204B TX and RX Transport Layer with Base and Transceiver (Design Example)

Avalon-ST

32 Bits per Channel

Serial Interface

(TX_n, TX_p)

Avalon-ST

32 Bits per Channel

Serial Interface

(RX_n, RX_p)

32-Bits Architecture

The JESD204B IP core consist of 32-bit internal datapath per lane. This means that JESD204B IP Core

expects the data samples to be assembled into 32-bit data (4 octets) per lane in the transport layer before

sending the data to the Avalon-ST data bus. The JESD204 IP core operates in the link clock domain. The

link clock runs at (data rate/40) because it is operating in 32-bit data bus after 8B/10B encoding.

As the internal datapath of the core is 32-bits, the (F × K) value must be in the order of 4 to align the

multi-frame length on a 32-bit boundary. Apart from this, the deterministic latency counter values such

as LMFC counter, RBD counter, and Subclass 2 adjustment counter will be in link clock count instead of

frame clock count.

Avalon-ST Interface

The JESD204 IP core and transport layer in the design example use the Avalon-ST source and sink

interfaces. There is no backpressure mechanism implemented in this core. The JESD204B IP core expects

continuous stream of data samples from the upstream device.

UG-01142

2015.05.04

JESD204B IP Core Functional Description

4-3

JESD204B IP Core Functional Description

Altera Corporation