Altera JESD204B IP User Manual

Page 75

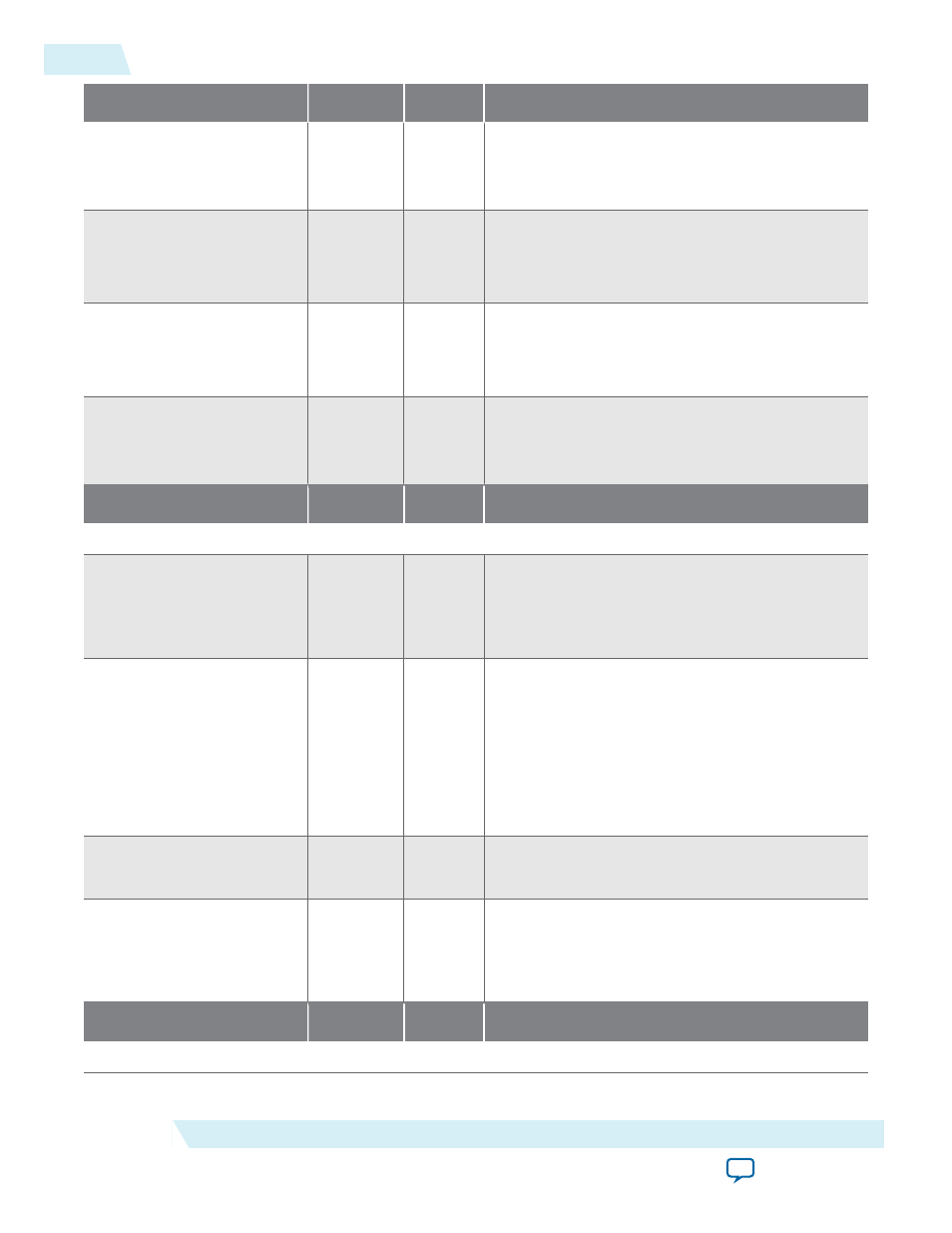

Signal

Width

Direction

Description

reconfig_avmm_

readdata[]

32

Output

The output data.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

reconfig_avmm_write

1

Input

Write signal. This signal is active high.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

reconfig_avmm_read

1

Input

Read signal. This signal is active high.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

reconfig_avmm_

waitrequest

1

Output

Wait request signal.

This signal is only available if you enable dynamic

reconfiguration for Arria 10 FPGA variants.

Signal

Width

Direction

Description

Avalon-ST Interface

jesd204_rx_link_data[]

L*32

Output

Indicates a 32-bit data from the DLL to the

transport layer. The data format is big endian,

where the earliest octet is placed in bit [31:24] and

the latest octet is placed in bit [7:0].

jesd204_rx_link_valid

1

Output

Indicates whether the data to the transport layer is

valid or invalid. The Avalon-ST source interface in

the RX core cannot be backpressured and will

transmit the data when the

jesd204_rx_data_

valid

signal is asserted.

• 0—data is invalid

• 1—data is valid

jesd204_rx_link_ready

1

Input

Indicates that the Avalon-ST sink interface in the

transport layer is ready to receive data.

jesd204_rx_frame_error

1

Input

Indicates an empty data stream due to invalid data.

This signal is asserted high to indicate an error

during data transfer from the RX core to the

transport layer.

Signal

Width

Direction

Description

Avalon-MM Interface

4-38

Receiver

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description