Altera JESD204B IP User Manual

Page 131

Advertising

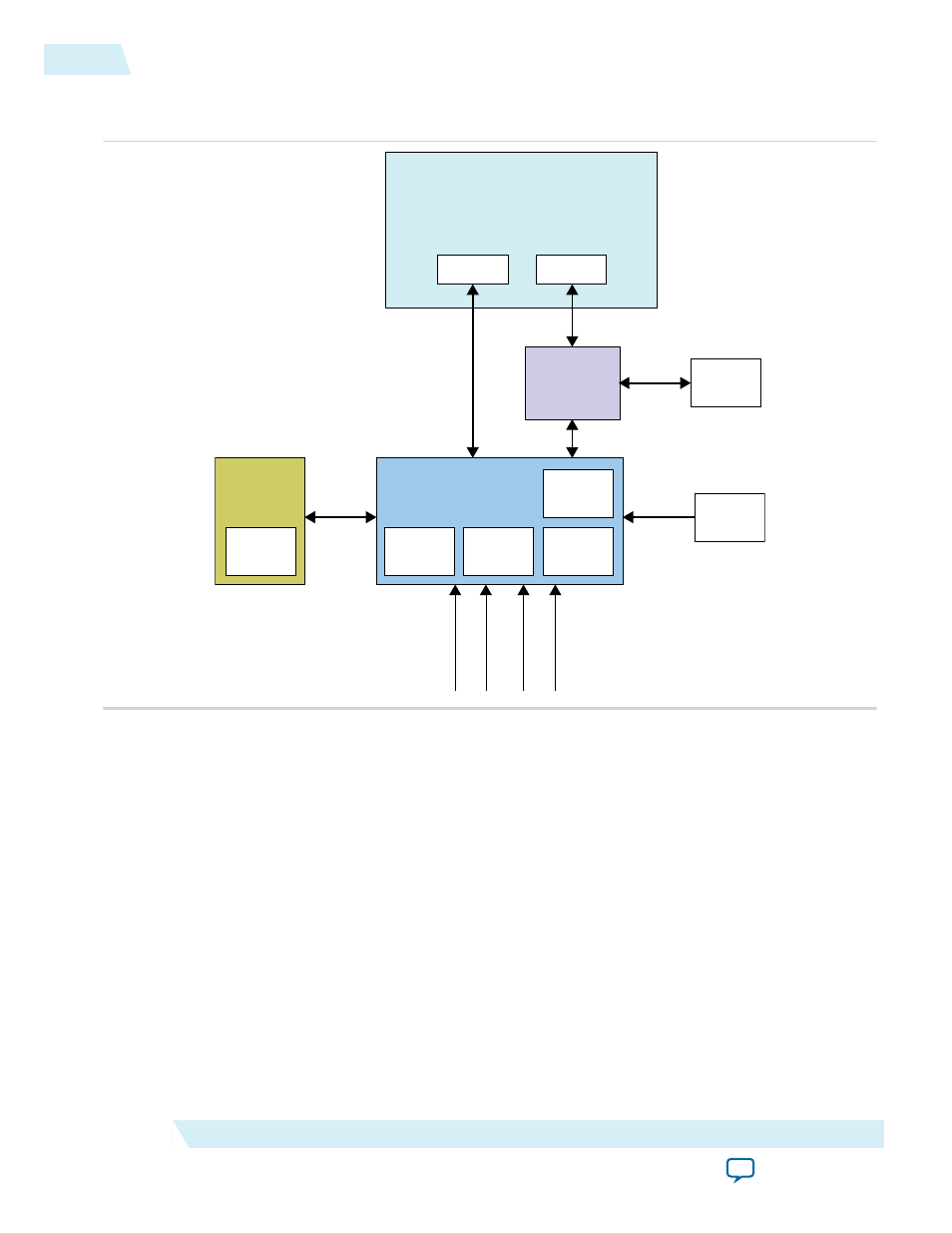

Figure 5-19: Dynamic Reconfiguration Block Diagram (For 28 nm Device Families—Stratix V and Arria

V)

JESD204B IP Core (Duplex)

CSR

PHY

PHY MIF

ROM

SPI Master

Clock MIF

ROM

DAC MIF

ROM

ADC MIF

ROM

JESD MIF

ROM

Control Unit

PLL MIF

ROM

PLL

Reconfiguration Avalon-MM

Avalon-MM

Transceiver

Reconfiguration

Controller

Avalon-MM

Avalon-MM

rec

onfig

run

time_lmf

run

time_datar

at

e

cu_busy

Avalon-MM

5-50

Dynamic Reconfiguration Operation

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Design Guidelines

Advertising