Altera JESD204B IP User Manual

Page 110

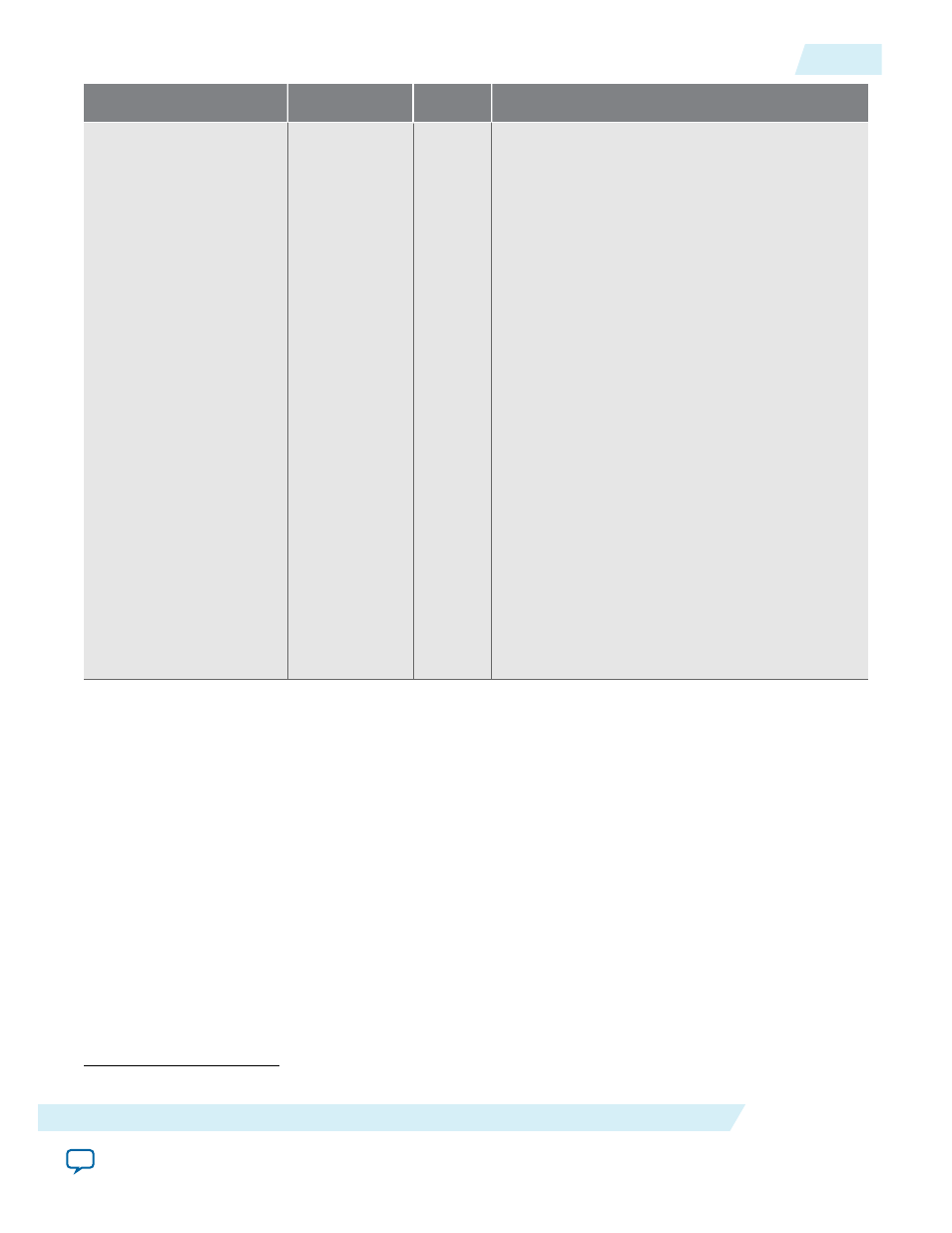

Signal

Clock Domain

Direction

Description

csr_l[4:0]

(35)

mgmt_clk

Input

Indicates the number of active lanes for the link.

This 5-bit bus represents the L value in zero-

based binary format. For example, if L = 1, the

csr_l[4:0]

= "00000". This design example

supports the following values:

• 00000

• 00001

• 00011

• 00111

Any programmed value beyond the supported

range may result in undeterminable behavior in

the transport layer. You must ensure that the

csr_l[4:0]

value always match the system

parameter L value.

Runtime reconfiguration supports L fallback. For

static configuration, set the maximum L and

reconfigure csr_l[] to a smaller value during

runtime. This transport layer only supports

higher index channels to be powered down. To

interleave the de-commision channels, you need

to modify the interface connection from the DLL

to transport layer.

Connect this signal to the RX DLL

csr_l[]

output pin.

(35)

This signal should be static and valid before the deassertion of the

link_rst_n

and

frame_rst_n

signals.

UG-01142

2015.05.04

RX Path

5-29

JESD204B IP Core Design Guidelines

Altera Corporation