Breaker failure logic 3 for standard relays (bfl3) – Basler Electric BE1-BPR User Manual

Page 38

2-14

BE1-BPR Application

9272000990 Rev J

3. Trip Coil Status Monitor. Preprogrammed logic is provided using IN1 to provide breaker status and

IN2 for trip coil continuity. Refer to Application Data in this section information for further details on

the circuit operation.

4. Breaker Arc Protection. Preprogrammed logic is provided using fault detector 3 (F3) for the MAF fault

detector, IN1 for breaker status, and OUT4 for the arc detector output. Refer to Application Data in

this section for further details on the circuit operation.

5. Retrip Output. A RETRIP output is provided to give a backup trip signal to the breaker trip coil. This

can either provide a separate path to a single trip coil or be hooked to the backup trip coil if available.

6. Alarm Output. An Alarm output is provided to signal relay failure or diagnostic alarm.

Figure 2-17. BFL2 Logic

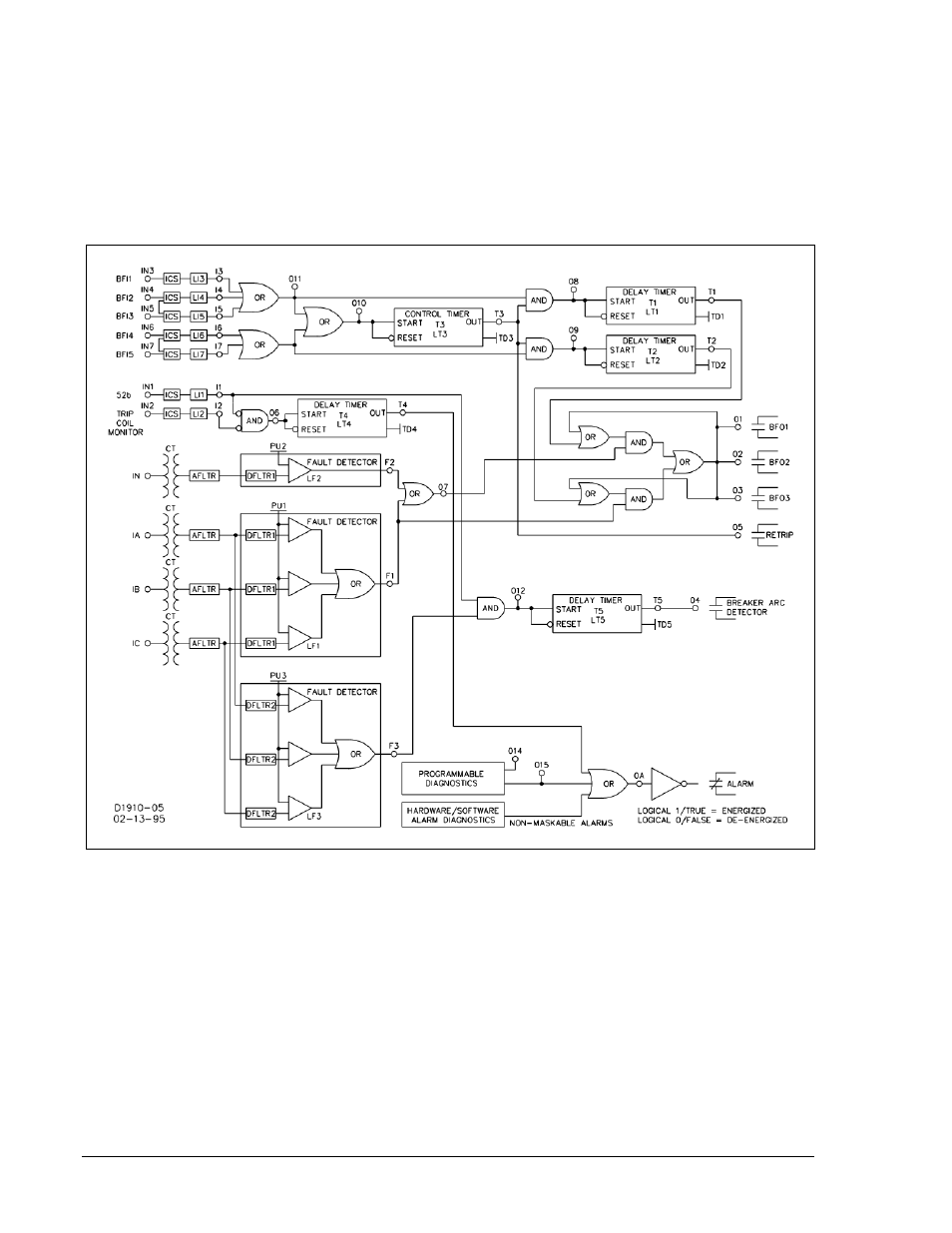

Breaker Failure Logic 3 for Standard Relays (BFL3)

BFL3 logic (shown in Figure 2-18) provides the following application features.

1. Three-Pole Tripping BF Logic (Features: Input/output latch-in provided and Control timer limits

operational window). Three BFI inputs are available at IN3, IN4, and IN5 to start delay timer T1. If the

BFI inputs are not reset by the time timer 1 times out and either the phase (F1) or neutral fault

detector (F2) is picked up, then BFO1-3 closes (OUT1-3), tripping the backup breakers. A control

timer (T3) is used to limit the breaker failure window of opportunity and latch-in the BFI inputs. Refer

to the breaker failure timing diagram in Section 1 for information on setting the delay and control

timers.

2. Single-Pole Tripping BF Logic (Features: Input/Output latch-in provided and Control timer limits

operational window). If single-pole tripping is used, two additional BFI inputs are available (IN6 and

IN7) to start delay timer T2. These inputs are only supervised by the phase fault detector (F1). If the

BFI (IN6 and IN7) inputs are not reset by the time the timer T2 times out and the phase fault detector