Reset details – Altera IP Compiler for PCI Express User Manual

Page 111

Chapter 5: IP Core Interfaces

5–25

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

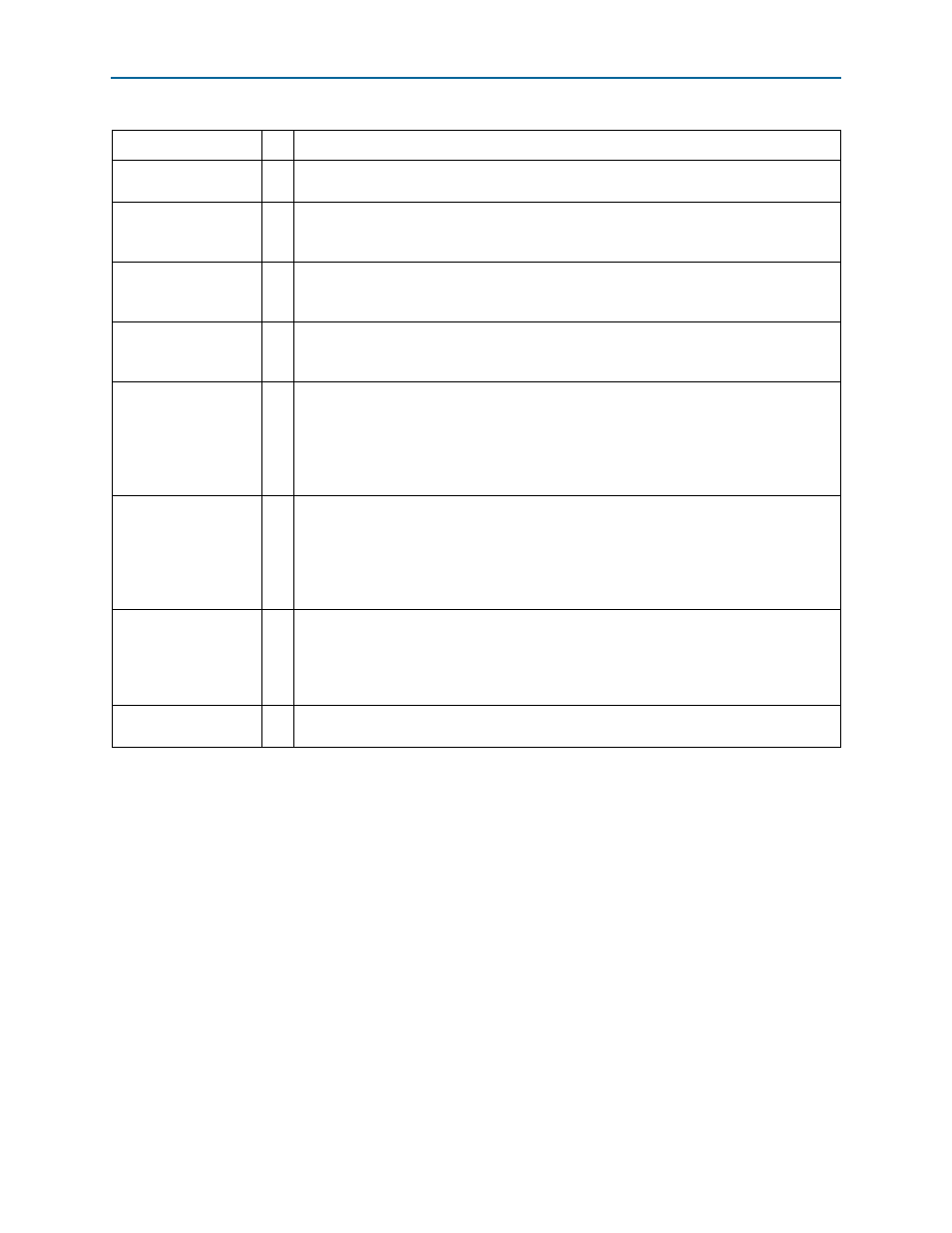

Reset Details

The hard IP implementation (×1, ×4, and ×8) or the soft IP implementation (×1 and

×4) have three reset inputs: npor, srst, and crst. npor is used internally for all sticky

registers that may not be reset in L2 low power mode or by the fundamental reset.

npor

is typically generated by a logical OR of the power-on-reset generator and the

perst

signal from the connector, as specified in the PCI Express card

electromechanical specification. The srst signal is a synchronous reset of the datapath

state machines. The crst signal is a synchronous reset of the nonsticky configuration

space registers. For endpoints, whenever the l2_exit, hotrst_exit, dlup_exit, or

other power-on-reset signals are asserted, srst and crst should be asserted for one or

more cycles for the soft IP implementation and for at least 2 clock cycles for hard IP

implementation.

rstn

I

Asynchronous reset of configuration space and datapath logic. Active Low. This signal is

only available on the ×8 IP core. Used in ×8 soft IP implementation only.

npor

I

Power on reset. This signal is the asynchronous active-low power-on reset signal. This reset

signal is used to initialize all configuration space sticky registers, PLL, and SERDES circuitry.

It also resets the datapath and control registers.

srst

I

Synchronous datapath reset. This signal is the synchronous reset of the datapath state

machines of the IP core. It is active high. This signal is only available on the hard IP and soft

IP ×1 and ×4 implementations.

crst

I

Synchronous configuration reset. This signal is the synchronous reset of the nonsticky

configuration space registers. It is active high. This signal is only available on the hard IP

implementation and the ×1 and ×4 soft IP implementations.

l2_exit

O

L2 exit. The PCI Express specification defines fundamental hot, warm, and cold reset states.

A cold reset (assertion of crst and srst for the hard IP implementation and the ×1 and ×4

soft IP implementation, or rstn for ×8 soft IP implementation) must be performed when the

LTSSM exits L2 state (signaled by assertion of this signal). This signal is active low and

otherwise remains high. It is asserted for one cycle (going from 1 to 0 and back to 1) after

the LTSSM transitions from l2_idl to detect.

hotrst_exit

O

Hot reset exit. This signal is asserted for 1 clock cycle when the LTSSM exits the hot reset

state. It informs the application layer that it is necessary to assert a global reset (crst and

srst

for the hard IP implementation and the ×1 and ×4 soft IP implementation, or rstn for

×8 soft IP implementation). This signal is active low and otherwise remains high. In Gen1

and Gen2, the hotrst_exit signal is asserted 1 ms after the ltssm signal exits the

hot.reset state

dlup_exit

O

This signal is active for one pld_clk cycle when the IP core exits the DLCSM DLUP state. In

endpoints, this signal should cause the application to assert a global reset (crst and srst

in the hard IP implementation and ×1 and ×4 soft IP implementation, or rstn in ×8 the soft

IP implementation). In root ports, this signal should cause the application to assert srst,

but not crst. This signal is active low and otherwise remains high.

rc_pll_locked

O

Indicates that the SERDES receiver PLL is in locked mode with the reference clock. In pipe

simulation mode this signal is always asserted.

Table 5–7. Reset and Link Training Signals (Part 2 of 2)

Signal

I/O

Description