Specifying exported interfaces – Altera IP Compiler for PCI Express User Manual

Page 297

Chapter 16: Qsys Design Example

16–9

Specifying Exported Interfaces

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

4. In the IRQ panel, click the connection from dma_0.irq to pcie_hard_ip_0.rxm_irq

and type 0.

Because the Qsys-generated IP Compiler for PCI Express implements an

individual interrupt scheme, you must specify the specific bit in the rxm_irq

interface to which each interrupt connects. In this case, the DMA controller’s

interrupt sender signal connects to bit 0 of the IP Compiler for PCI Express input

interrupt bus.

Specifying Exported Interfaces

To make them visible outside the Qsys system, you must export the remaining

interfaces of the IP Compiler for PCI Express Qsys component pcie_hard_ip_0. After

an interface is exported, it can connect to modules outside the Qsys system.

Follow these steps to export an interface:

1. In the row for the interface you want to export, click the Export column.

2. Accept the default name that appears in the Export column by clicking outside the

cell without modifying the text.

Export the pcie_hard_ip_0 interfaces listed in

.

pcie_hard_ip_0 bar2 Avalon-MM Master

dma_0 control_port_slave Avalon-MM Slave

pcie_hard_ip_0 bar2 Avalon-MM Master

pcie_hard_ip_0 cra Avalon-MM Slave

dma_0 irq Interrupt Sender

pcie_hard_ip_0 rxm_irq Interrupt Receiver

dma_0 read_master Avalon-MM Master

onchip_memory_0 s1 Avalon-MM Slave

dma_0 read_master Avalon-MM Master

pcie_hard_ip_0 txs Avalon-MM Slave

dma_0 write_master Avalon-MM Master

onchip_memory_0 s1 Avalon-MM Slave

dma_0 write_master Avalon-MM Master

pcie_hard_ip_0 txs Avalon-MM Slave

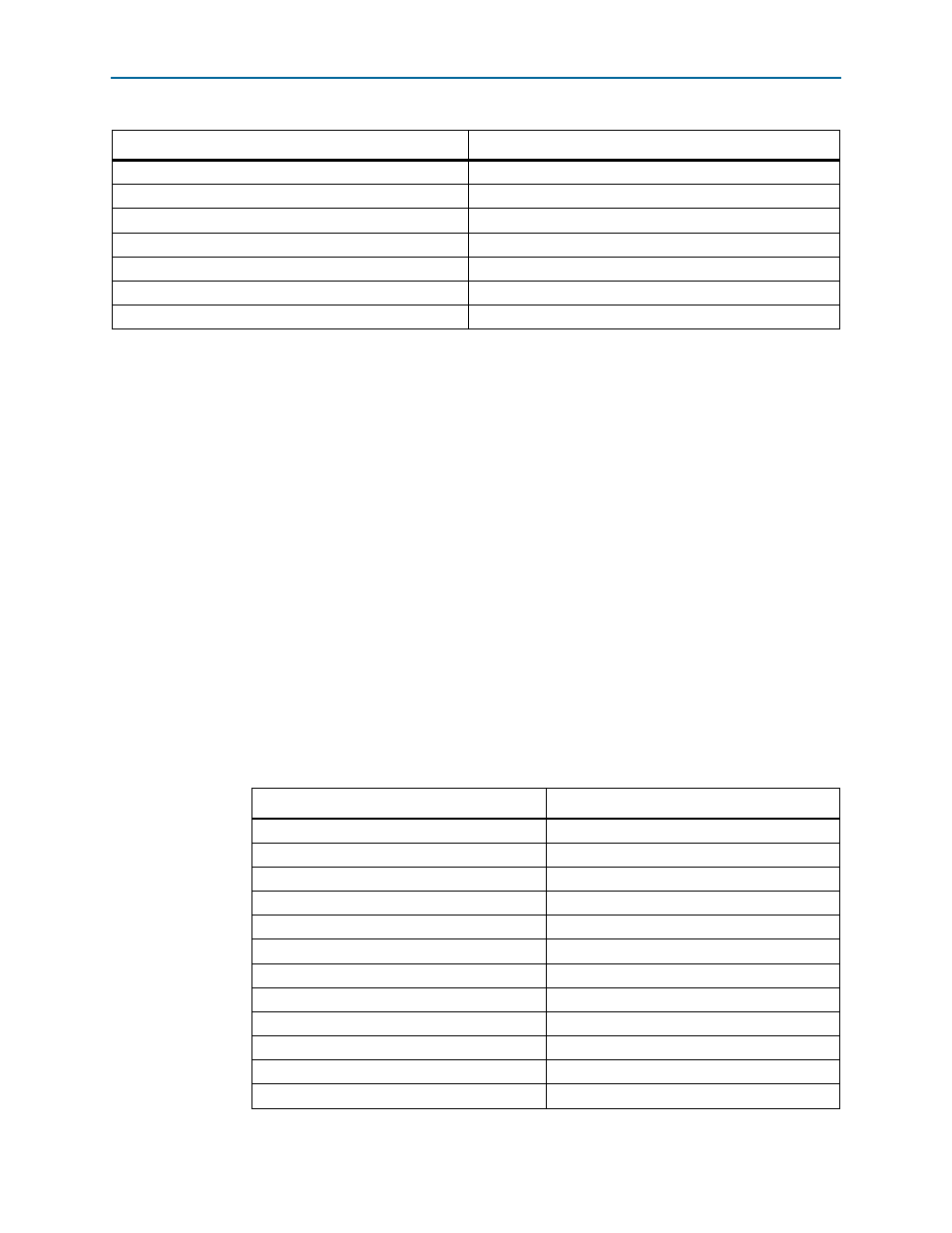

Table 16–10. Complete List of Qsys Connections (Part 2 of 2)

Make Connection From:

To:

Table 16–11. pcie_hard_ip_0 Exported Interfaces (Part 1 of 2)

Interface Name

Exported Name

cal_blk_clk

pcie_hard_ip_0_cal_blk_clk

refclk

pcie_hard_ip_0_refclk

test_in

pcie_hard_ip_0_test_in

pcie_rstn

pcie_hard_ip_0_pcie_rstn

clocks_sim

pcie_hard_ip_0_clocks_sim

reconfig_busy

pcie_hard_ip_0_reconfig_busy

pipe_ext

pcie_hard_ip_0_pipe_ext

test_out

pcie_hard_ip_0_test_out

rx_in

pcie_hard_ip_0_rx_in

tx_out

pcie_hard_ip_0_tx_out

reconfig_togxb

pcie_hard_ip_0_reconfig_togxb

reconfig_gxbclk

pcie_hard_ip_0_reconfig_gxbclk