Reset soft ip implementation – Altera IP Compiler for PCI Express User Manual

Page 168

7–4

Chapter 7: Reset and Clocks

Reset Soft IP Implementation

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

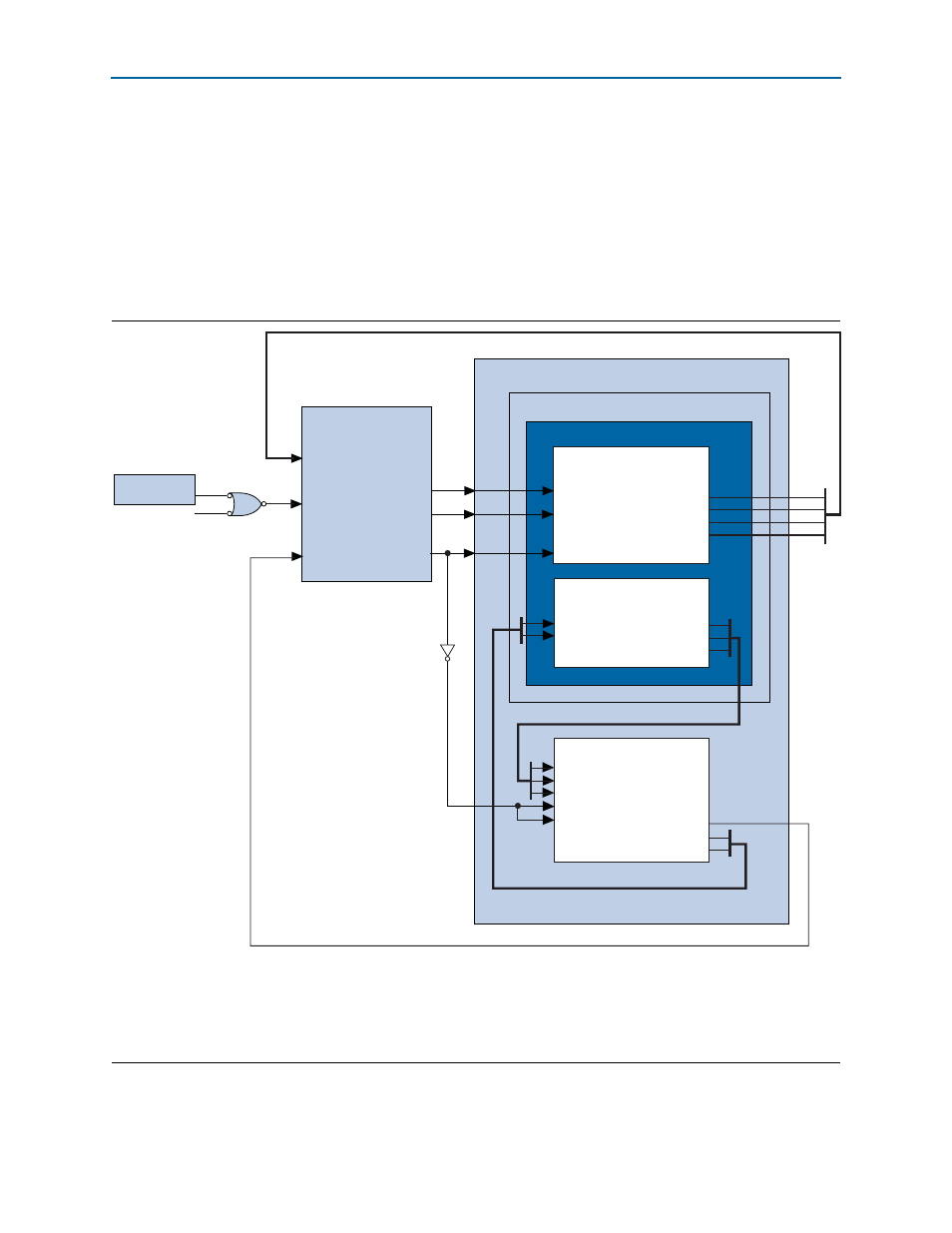

Reset Soft IP Implementation

shows the global reset signals for ×1 and ×4 endpoints in the soft IP

implementation. To use this variant, you must design the logic to implement reset and

calibration. For designs that use the internal ALTGX transceiver, the PIPE interface is

transparent. You can use the reset sequence provided for the hard IP implementation

in the <variant>_rs_hip.v or .vhd IP core as a reference in designing your own circuit.

In addition, to understand the domain of each reset signal, refer to

Figure 7–3. Global Reset Signals for ×1 and ×4 Endpoints in the Soft IP Implementation

Notes to

(1) The Gen1 ×8 does not include the crst signal and rstn replaces srst in the soft IP implementation.

(2) The dlup_exit signal should cause the application to assert srst, but not crst.

(3) gxb_powerdown stops the generation of core_clk_out for hard IP implementations and clk125_out for soft IP implementations.

(4) The rx_freqlocked signal is only used in Gen2 ×4 and Gen2 ×8 IP Compiler for PCI Express variations.

<variant>.v or .vhd

<variant>_core.v or .vhd

<variant>

_serdes.v or .vhd

SERDES Reset Controller

srst

crst

altpcie_hip_pipen1b.v or .vhd

Other Power

On Reset

perst#

l2_exit

tx_digitalreset

rx_analogreset

rx_digitalreset

tx_digitalreset

rx_analogreset

rx_digitalreset

npor

pll_locked

rx_pll_locked

pll_powerdown

gxb_powerdown

rx_freqlocked

Note (1)

Note (4)

Note (1)

Note (2)

Note (3)

rx_freqlocked

pll_locked

rx_pll_locked

hotrst_exit

dlup_exit

dl_ltssm[4:0]

Reset Synchronization

Circuitry from Design

Example