Altera IP Compiler for PCI Express User Manual

Page 293

Chapter 16: Qsys Design Example

16–5

Parameterizing the IP Compiler for PCI Express

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

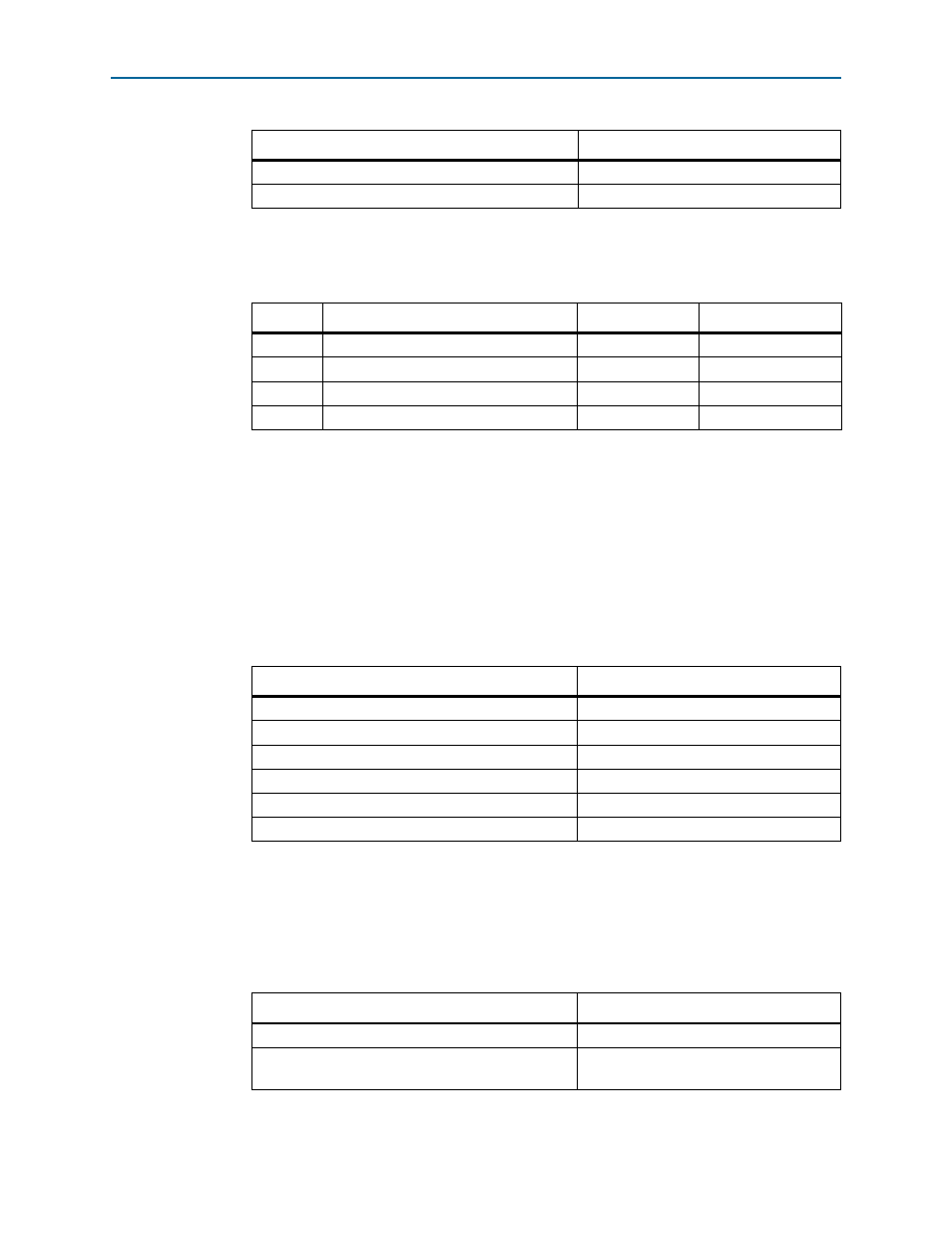

2. Under the PCI Base Address Registers (Type 0 Configuration Space) heading,

specify the settings in

.

1

You cannot fill in the Bar Size or Avalon Base Address in the IP Compiler for PCI

Express parameter editor. Qsys calculates the Bar Size from the size of the

Avalon-MM slave port to which the BAR is connected. After you add components to

your Qsys system, you can use the Auto-Assign Base Addresses function on the

System menu to define the address map.

3. Under the Device Identification Registers heading, specify the values in

. After you configure your device, the values you specify in the

parameter editor can be read by software from these read-only registers.

4. Under the Link Capabilities heading, leave Link port number at its default value

of 1.

5. Under the Error Reporting heading, leave all types of error reporting turned off.

6. Under the Buffer Configuration heading, specify the settings in

.

Use 62.5 MHz application clock

Leave this option off

Test out width

64 bits

Table 16–3. PCI Base Address Registers (Type 0 Configuration Space)

BAR

BA

BAR Size

Avalon Base Address

0

64-bit Prefetchable Memory

Auto

Auto

1

Not used

—

—

2

32 bit Non-Prefetchable

Auto

Auto

3–5

Not used

—

—

Table 16–2. IP Compiler for PCI Express System Settings (Part 2 of 2)

Parameter

Value

Table 16–4. Device Identification Registers

Parameter

Value

Vendor ID

0x00001172

Device ID

0x00000004

Revision ID

0x00000001

Class code

0x00FF0000

Subsystem vendor ID

0x00001172

Subsystem ID

0x00000004

Table 16–5. Buffer Configuration Settings

Parameter

Value

Maximum payload size

256 Bytes

RX buffer credit allocation –

performance for received requests

High