Altera IP Compiler for PCI Express User Manual

Page 50

3–14

Chapter 3: Parameter Settings

IP Core Parameters

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

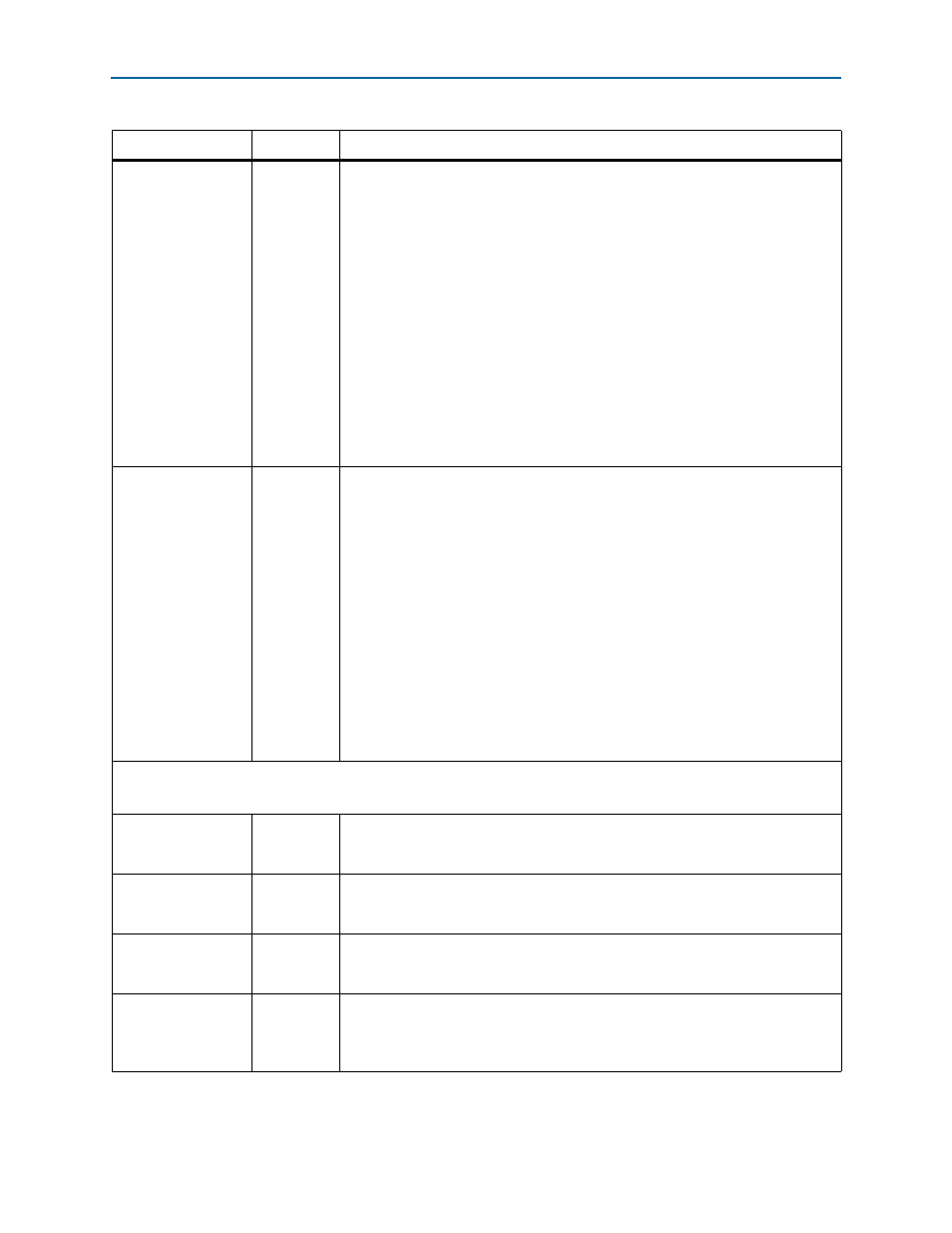

Completion

timeout range

Ranges A–D

This option is only available for PCI Express version 2.0 and higher. It indicates

device function support for the optional completion timeout programmability

mechanism. This mechanism allows system software to modify the completion

timeout value. This field is applicable only to root ports and endpoints that issue

requests on their own behalf. Completion timeouts are specified and enabled via the

Device Control 2 register (0x0A8) of the PCI Express Capability Structure Version 2.0

described in

. For all other functions this field is reserved and

must be hardwired to 0x0. Four time value ranges are defined:

Range A: 50 µs to 10 ms

Range B: 10 ms to 250 ms

Range C: 250 ms to 4 s

Range D: 4 s to 64 s

Bits are set according to the list below to show timeout value ranges supported. 0x0

completion timeout programming is not supported and the function must implement

a timeout value in the range 50 s to 50 ms.

Completion

timeout range

(continued)

Each range is turned on or off to specify the full range value. Bit 0 controls Range A,

bit 1 controls Range B, bit 2 controls Range C, and bit 3 controls Range D. The

following values are supported:

0x1: Range A

0x2: Range B

0x3: Ranges A and B

0x6: Ranges B and C

0x7: Ranges A, B, and C

0xE: Ranges B, C and D

0xF: Ranges A, B, C, and D

All other values are reserved. This parameter is not available for PCIe version 1.0.

Altera recommends that the completion timeout mechanism expire in no less than

10 ms.

Error Reporting

Implement

advanced error

reporting

On/Off

Implements the advanced error reporting (AER) capability.

Implement ECRC

check

On/Off

Enables ECRC checking capability. Sets the read-only value of the ECRC check

capable bit in the advanced error capabilities and control register. This parameter

requires you to implement the advanced error reporting capability.

Implement ECRC

generation

On/Off

Enables ECRC generation capability. Sets the read-only value of the ECRC generation

capable bit in the advanced error capabilities and control register. This parameter

requires you to implement the advanced error reporting capability.

Implement ECRC

forwarding

On/Off

Available for hard IP implementation only. Forward ECRC to the application layer. On

the Avalon-ST receive path, the incoming TLP contains the ECRC dword and the TD

bit is set if an ECRC exists. On the Avalon-ST transmit path, the TLP from the

application must contain the ECRC dword and have the TD bit set.

Table 3–11. Capabilities Parameters (Part 2 of 4)

Parameter

Value

Description