The lmi interface – Altera IP Compiler for PCI Express User Manual

Page 61

Chapter 4: IP Core Architecture

4–3

Application Interfaces

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

The PCI Express Avalon-ST adapter maps PCI Express transaction layer packets

(TLPs) to the user application RX and TX busses.

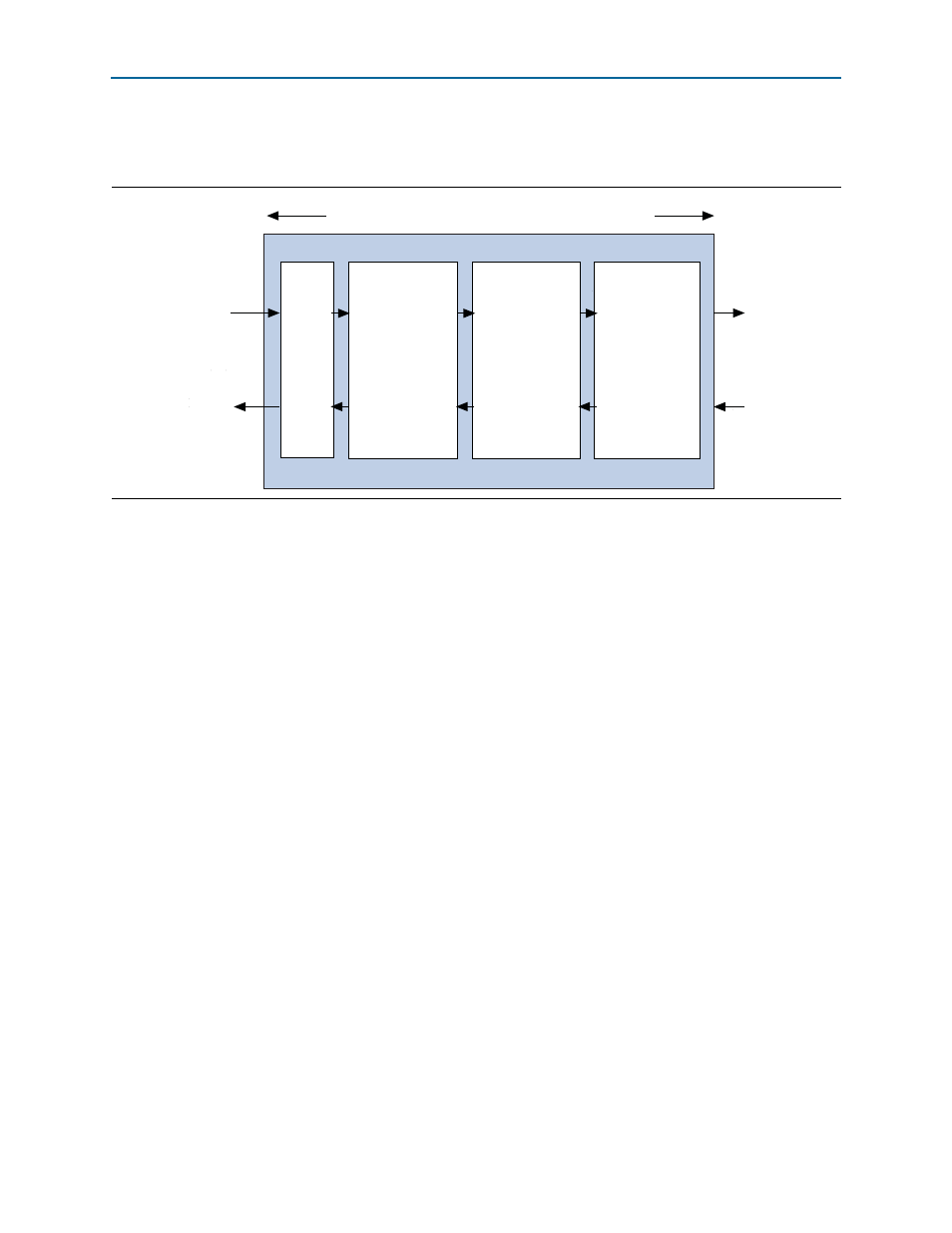

illustrates this interface.

In both the hard IP and soft IP implementations of the IP Compiler for PCI Express,

the adapter maps the user application Avalon-ST interface to PCI Express TLPs. The

hard IP and soft IP implementations differ in the following respects:

■

The hard IP implementation includes dedicated clock domain crossing logic

between the PHYMAC and data link layers. In the soft IP implementation you can

specify one or two clock domains for the IP core.

■

The hard IP implementation includes the following interfaces to access the

configuration space registers:

■

The LMI interface

■

The Avalon-MM PCIe reconfig bus which can access any read-only

configuration space register

■

In root port configuration, you can also access the configuration space registers

with a configuration type TLP using the Avalon-ST interface. A type 0

configuration TLP is used to access the RP configuration space registers, and a

type 1 configuration TLP is used to access the configuration space registers of

downstream nodes, typically endpoints on the other side of the link.

Figure 4–2. IP Core with PCI Express Avalon-ST Interface Adapter

Tx

Rx

Transaction Layer

Data Link Layer

Physical Layer

IP Compiler for PCI Express

To Application Layer

To Link

Avalon-ST

Tx Port

Avalon-ST

Rx Port

Avalon-ST

Adapter

With information sent

by the application

layer, the transaction

layer generates a TLP,

which includes a

header and, optionally,

a data payload.

The data link layer

ensures packet

integrity, and adds a

sequence number and

link cyclic redundancy

code (LCRC) check to

the packet.

The physical layer

encodes the packet

and transmits it to the

receiving device on the

other side of the link.

The transaction layer

disassembles the

transaction and

transfers data to the

application layer in a

form that it recognizes.

The physical layer

decodes the packet

and transfers it to the

data link layer.

The data link layer

verifies the packet's

sequence number and

checks for errors.