Ebfm_cfgrd_wait procedure – Altera IP Compiler for PCI Express User Manual

Page 270

15–38

Chapter 15: Testbench and Design Example

BFM Procedures and Functions

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

ebfm_cfgrd_wait Procedure

The ebfm_cfgrd_wait procedure reads up to four bytes of data from the specified

configuration register and stores the data in BFM shared memory. This procedure

waits until the read completion has been returned.

Arguments

bus_num

PCI Express bus number of the target device.

dev_num

PCI Express device number of the target device.

fnc_num

Function number in the target device to be accessed.

regb_ad

Byte-specific address of the register to be written.

regb_ln

Length, in bytes, of the data written. Maximum length is four bytes, The regb_ln the

regb_ad

arguments cannot cross a DWORD boundary.

imm_data

Data to be written

In VHDL. this argument is a std_logic_vector(31 downto 0).

In Verilog HDL, this argument is reg [31:0].

In both languages, the bits written depend on the length:

Length

Bits Written

4

[31:0]

3

[23:0]

2

[15:0]

1

[7:0]

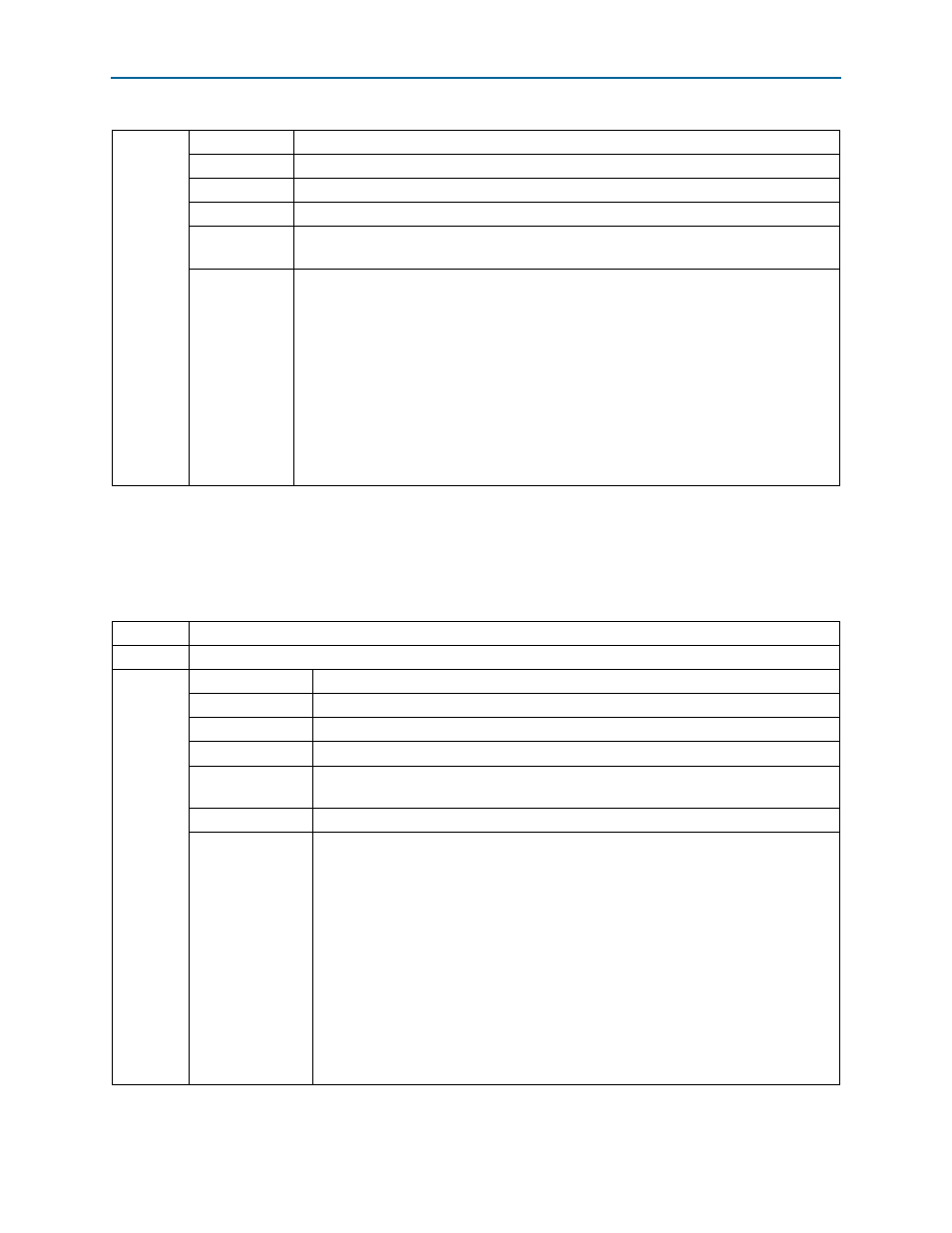

Table 15–28. ebfm_cfgwr_imm_nowt Procedure (Part 2 of 2)

Table 15–29. ebfm_cfgrd_wait Procedure

Location

altpcietb_bfm_rdwr.v or altpcietb_bfm_rdwr.vhd

Syntax

ebfm_cfgrd_wait(bus_num, dev_num, fnc_num, regb_ad, regb_ln, lcladdr, compl_status)

Arguments

bus_num

PCI Express bus number of the target device.

dev_num

PCI Express device number of the target device.

fnc_num

Function number in the target device to be accessed.

regb_ad

Byte-specific address of the register to be written.

regb_ln

Length, in bytes, of the data read. Maximum length is four bytes. The regb_ln and the

regb_ad

arguments cannot cross a DWORD boundary.

lcladdr

BFM shared memory address of where the read data should be placed.

compl_status

Completion status for the configuration transaction.

In VHDL, this argument is a std_logic_vector(2 downto 0) and is set by the

procedure on return.

In Verilog HDL, this argument is reg [2:0].

In both languages, this is the completion status as specified in the PCI Express

specification:

Compl_StatusDefinition

000SC— Successful completion

001UR— Unsupported Request

010CRS — Configuration Request Retry Status

100CA — Completer Abort