Altera IP Compiler for PCI Express User Manual

Page 121

Chapter 5: IP Core Interfaces

5–35

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

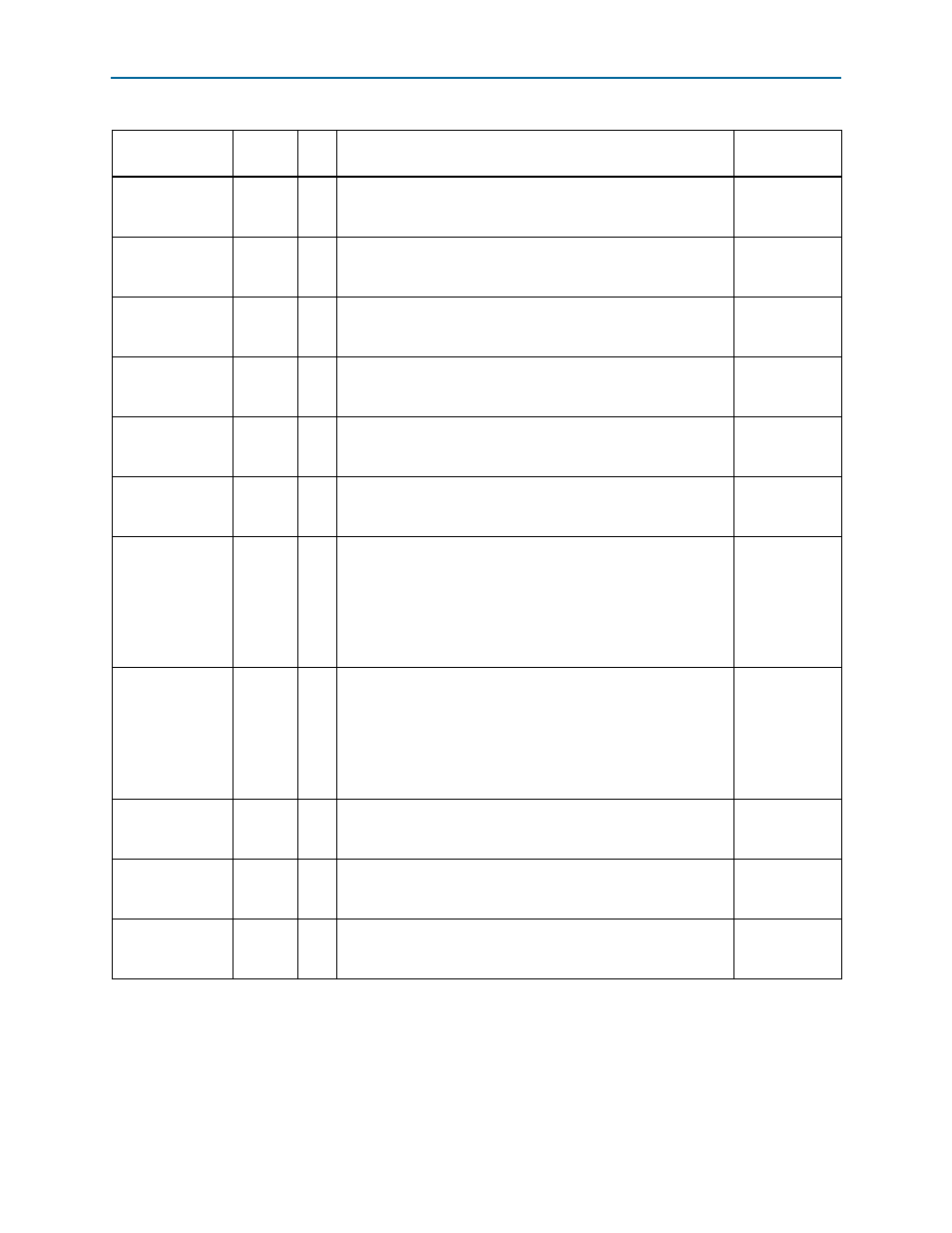

cfg_secbus

8

O

Secondary bus number. Available in root port mode.

0x018

cfg_subbus

8

O

Subordinate bus number. Available in root port mode.

0x018

cfg_io_bas

20

O

IO base windows of the Type1 configuration space. This register is

only available in root port mode.

0x01C

cfg_io_lim

20

O

IO limit windows of the Type1 configuration space. This register is

only available in root port mode.

0x01C

cfg_np_bas

12

O

Non-prefetchable base windows of the Type1 configuration space.

This register is only available in root port mode.

EXP ROM

cfg_np_lim

12

O

Non-prefetchable limit windows of the Type1 configuration space.

This register is only available in root port mode.

EXP ROM

cfg_pr_bas

44

O

Prefetchable base windows of the Type1 configuration space. This

register is only available in root port mode.

0x024

Prefetchable

memory

cfg_pr_lim

12

O

Prefetchable limit windows of the Type1 configuration space.

Available in root port mode.

0x024

Prefetchable

memory

cfg_pmcsr

32

O

cfg_pmcsr[31:16]

is power management control and

cfg_pmcsr[15:0]

the power management status register. This

register is only available in root port mode.

0x07C

cfg_msixcsr

16

O

MSI-X message control. Duplicated for each function

implementing MSI-X.

0x068

cfg_msicsr

16

O

MSI message control. Duplicated for each function implementing

MSI.

0x050

Table 5–15. Configuration Space Register Descriptions (Part 2 of 3)

Register

Width

Dir

Description

Register

Reference