Altera IP Compiler for PCI Express User Manual

Page 116

5–30

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

The configuration space signals provide access to some of the control and status

information available in the configuration space registers; these signals provide access

to unused registers that are labeled reserved in the

. This interface is synchronous to core_clk. To access the configuration

space from the application layer, you must synchronize to the application layer clock.

describes the configuration space interface and hot plug signals that are

available in the hard IP implementation. Refer to Chapter 6 of the

e information about the hot plug signals.

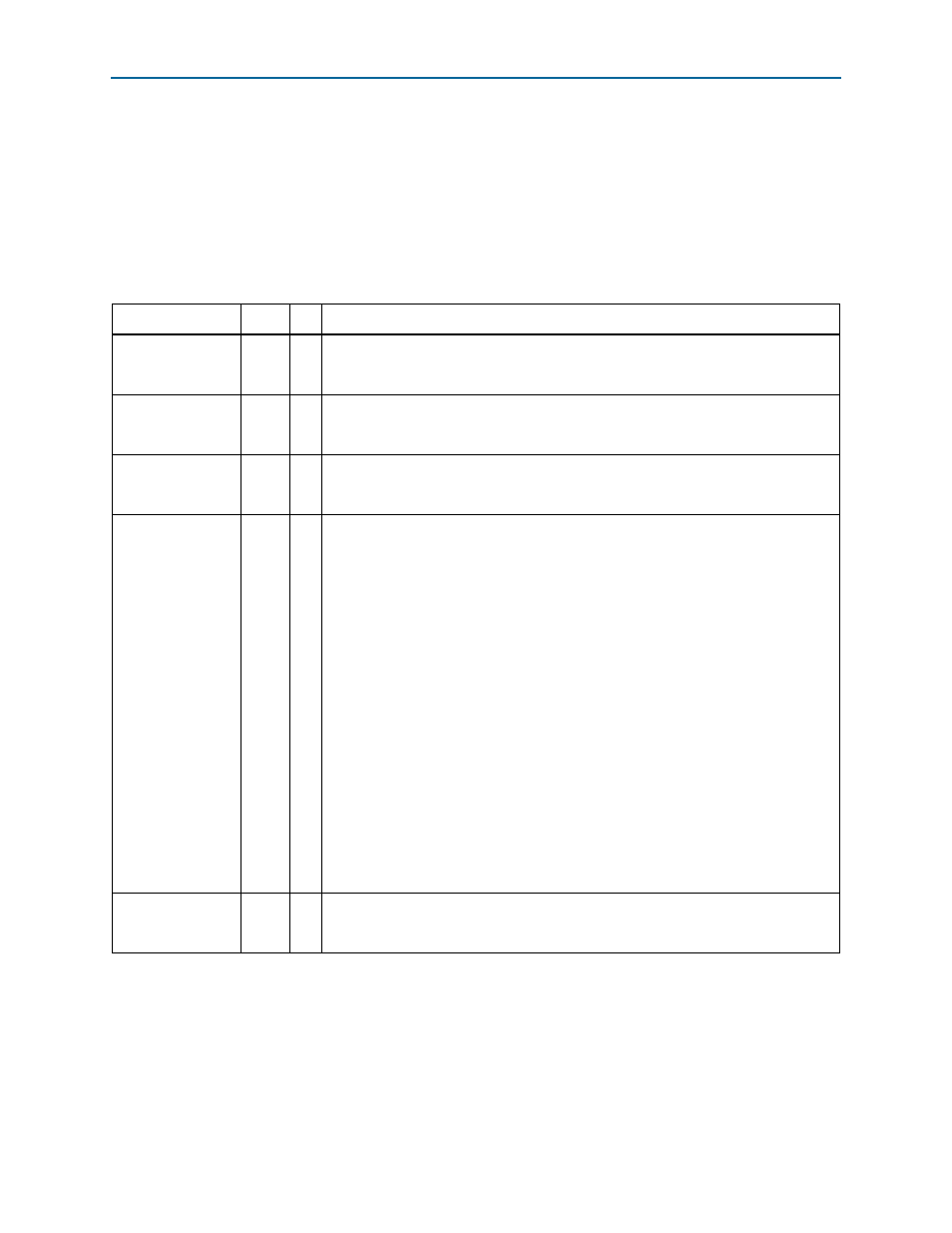

Table 5–13. Configuration Space Signals (Hard IP Implementation) (Part 1 of 2)

Signal

Width

Dir

Description

tl_cfg_add

4

0

Address of the register that has been updated. This address space is described in

. The information updates every 8 core_clks along with

tl_cfg_ctl

.

tl_cfg_ctl

32

0

The tl_cfg_ctl signal is multiplexed and contains the contents of the configuration

space registers shown in

. This register carries data that

updates every 8 core_clk cycles.

tl_cfg_ctl_wr

1

0

Write signal. This signal toggles when tl_cfg_ctl has been updated (every 8

core_clk

cycles). The toggle edge marks where the tl_cfg_ctl data changes. You

can use this edge as a reference to determine when the data is safe to sample.

tl_cfg_sts

53

0

Configuration status bits. This information updates every 8 core_clk cycles. The

cfg_sts

group consists of (from MSB to LSB):

tl_cfg_sts[52:49]

= cfg_devcsr[19:16]error detection signal as follows:

[correctable error reporting, enable, non-fatal error reporting

enable,

fatal error reporting enable, unsupported request

reporting enable

]

tl_cfg_sts[48]

= cfg_slotcsr[24]Data link layer state changed

tl_cfg_sts[47]

= cfg_slotcsr[20]Command completed

tl_cfg_sts[46:31]

= cfg_linkcsr[31:16]Link status bits

tl_cfg_sts[30]

= cfg_link2csr[16]Current de-emphasis level.

cfg_link2csr[31:17]

are reserved per the PCIe Specification and are not

available on tl_cfg_sts bus

tl_cfg_sts[29:25]

= cfg_prmcsr[31:27]5 primary command status error bits

tl_cfg_sts[24]

= cfg_prmcsr[24]6th primary command status error bit

tl_cfg_sts[23:6]

= cfg_rootcsr[25:8]PME bits

tl_cfg_sts[5:1]

= cfg_seccsr[31:27] 5 secondary command status error bits

tl_cfg_sts[0]

= cfg_seccsr[24] 6th secondary command status error bit

tl_cfg_sts_wr

1

0

Write signal. This signal toggles when tl_cfg_sts has been updated (every 8

core_clk

cycles). The toggle marks the edge where tl_cfg_sts data changes. You

can use this edge as a reference to determine when the data is safe to sample.