Altera IP Compiler for PCI Express User Manual

Page 9

Chapter 1: Datasheet

1–7

General Description

August 2014

Altera Corporation

The IP Compiler for PCI Express supports ×1, ×2, ×4, and ×8 variations (

) that are suitable for either root port or endpoint applications. You can use

the parameter editor to customize the IP core. The Qsys design flows do not support

root port variations.

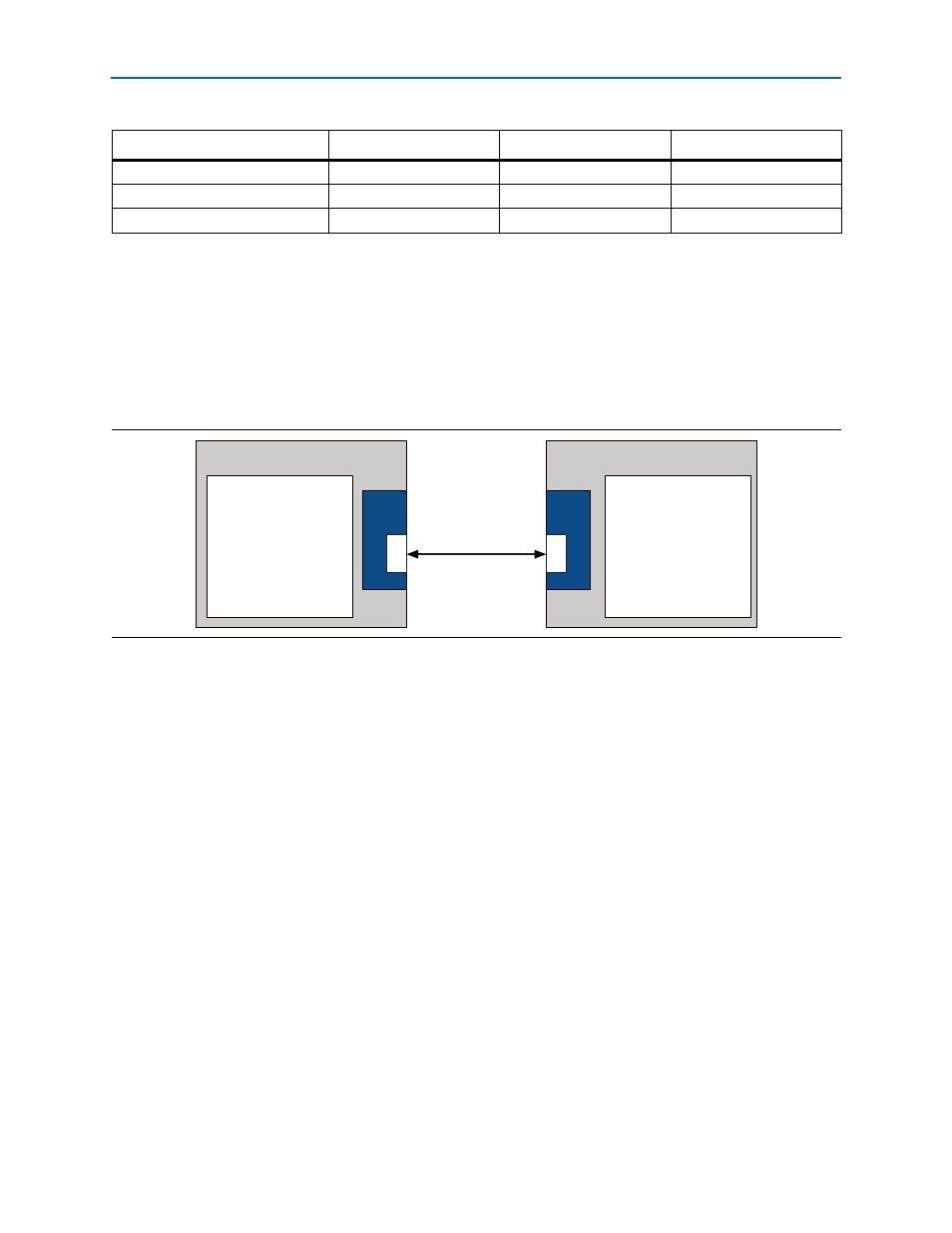

shows a relatively simple application that includes

two IP Compilers for PCI Express, one configured as a root port and the other as an

endpoint.

Arria II GZ

16 KBytes

16 KBytes

2 KBytes

Cyclone IV GX

4 KBytes

2 KBytes

256 Bytes

Stratix IV GX

16 KBytes

16 KBytes

2 KBytes

Table 1–6. IP Compiler for PCI Express Buffer and Payload Information (Part 2 of 2)

Devices Family

Total RX Buffer Space

Retry Buffer

Max Payload Size

Figure 1–2. PCI Express Application with a Single Root Port and Endpoint

Altera FPGA with Embedded

PCIe Hard IP Block

User Application

Logic

PCIe

Hard IP

Block

PCIe

Hard IP

Block

RP

EP

User Application

Logic

PCI Express Link

Altera FPGA with Embedded

PCIe Hard IP Block