Altera IP Compiler for PCI Express User Manual

Page 51

Chapter 3: Parameter Settings

3–15

IP Core Parameters

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

MSI Capabilities

–

MSI messages

requested

1, 2, 4, 8,

16, 32

Indicates the number of messages the application requests. Sets the value of the

multiple message capable field of the message control register, 0x050[31:16]. The

Qsys design flow supports only 1 MSI.

MSI message

64–bit address

capable

On/Off

Indicates whether the MSI capability message control register is 64-bit addressing

capable. PCI Express native endpoints always support MSI 64-bit addressing.

Link Capabilities

Link common clock

On/Off

Indicates if the common reference clock supplied by the system is used as the

reference clock for the PHY. This parameter sets the read-only value of the slot clock

configuration bit in the link status register.

Data link layer active

reporting

On/Off

Turn this option On for a downstream port if the component supports the optional

capability of reporting the DL_Active state of the Data Link Control and Management

State Machine. For a hot-plug capable downstream port (as indicated by the Hot-

Plug Capable

field of the Slot Capabilities register), this option must be

turned on. For upstream ports and components that do not support this optional

capability, turn this option Off. Endpoints do not support this option.

Surprise down

reporting

On/Off

When this option is On, a downstream port supports the optional capability of

detecting and reporting the surprise down error condition.

Link port number

0x01

Sets the read-only value of the port number field in the link capabilities register.

Slot Capabilities

Enable slot

capability

On/Off

The slot capability is required for root ports if a slot is implemented on the port. Slot

status is recorded in the PCI Express Capabilities register. This capability is

only available for root port variants. Therefore, this option is not available in the Qsys

design flow.

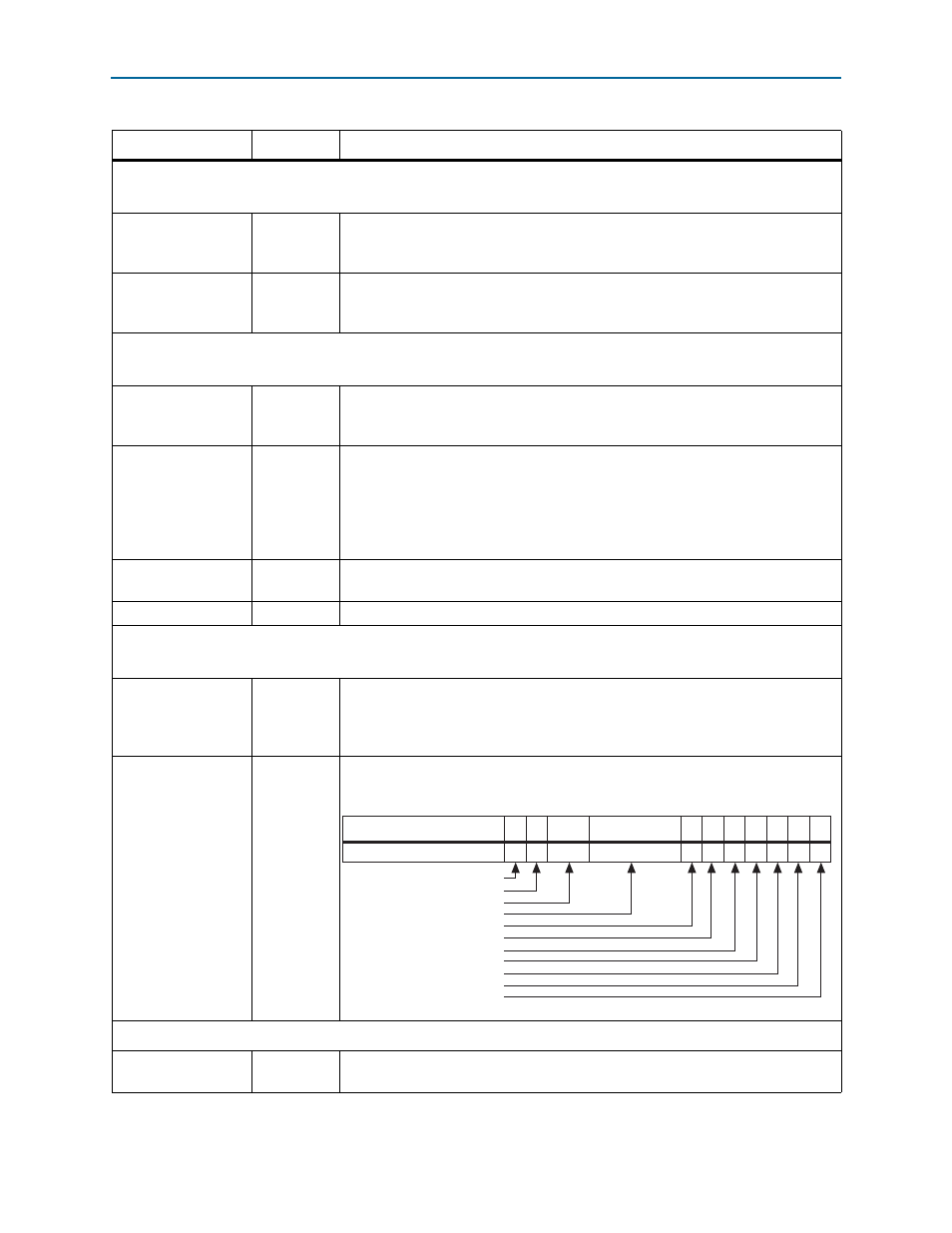

Slot capability

register

0x00000000

Defines the characteristics of the slot. You turn this option on by selecting Enable

slot capability. The various bits are defined as follows:

MSI-X Capabilities (0x68, 0x6C, 0x70)

Implement MSI-X

On/Off

The MSI-X functionality is only available in the hard IP implementation. The Qsys

design flow does not support MSI-X functionality.

Table 3–11. Capabilities Parameters (Part 3 of 4)

Parameter

Value

Description

31

19 18 17 16 15 14

7 6

5

Physical Slot Number

No Command Completed Support

Electromechanical Interlock Present

Slot Power Limit Scale

Slot Power Limit Value

Hot-Plug Capable

Hot-Plug Surprise

Power Indicator Present

Attention Indicator Present

MRL Sensor Present

Power Controller Present

Attention Button Present

0

4

3

2

1