Viewing the generated files – Altera IP Compiler for PCI Express User Manual

Page 26

2–10

Chapter 2: Getting Started

Viewing the Generated Files

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

9. On the Summary tab, select the files you want to generate. A gray checkmark

indicates a file that is automatically generated. All other files are optional.

10. Click Finish to generate the IP core, testbench, and supporting files.

1

A report file, <variation name>.html, in your project directory lists each file

generated and provides a description of its contents.

Viewing the Generated Files

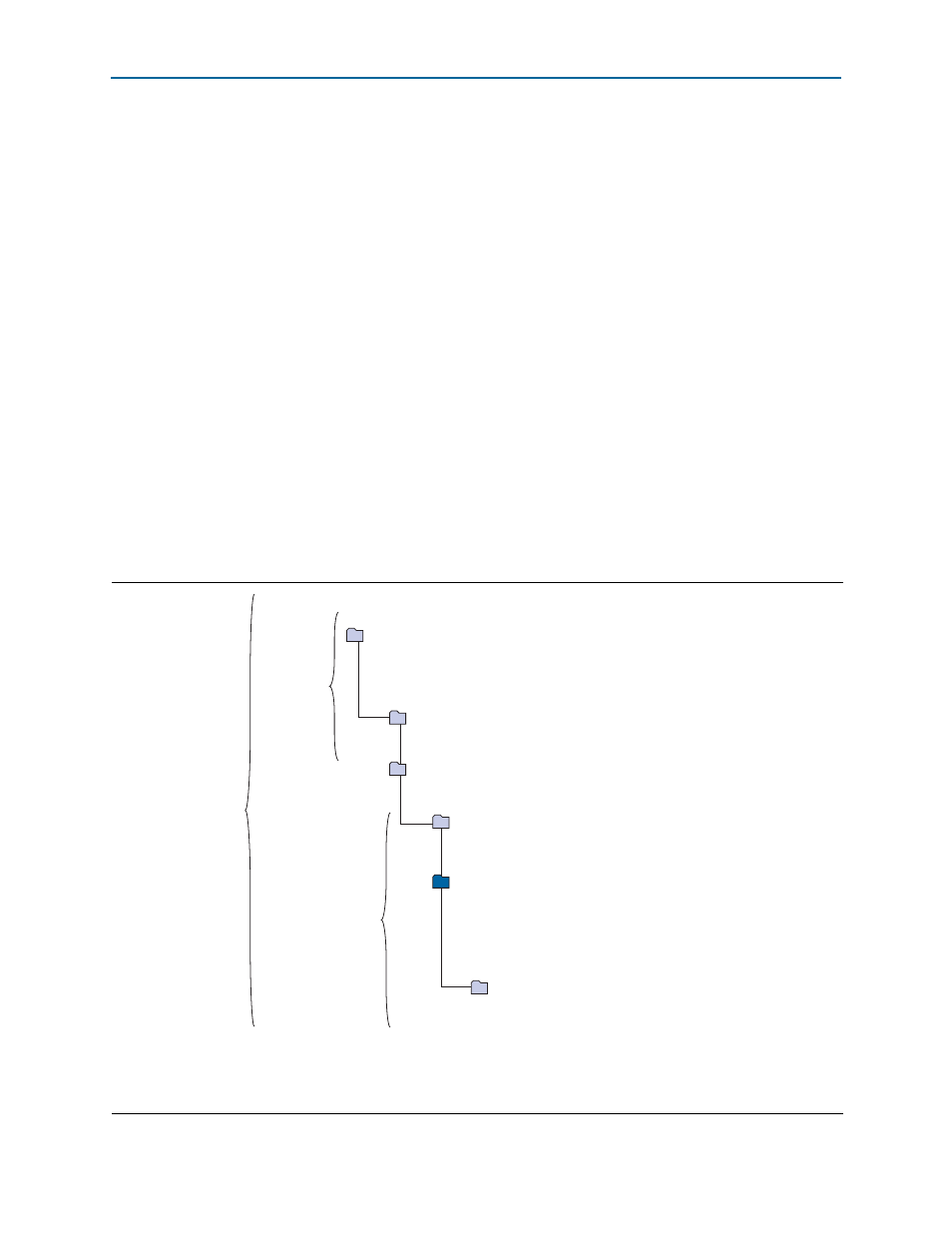

illustrates the directory structure created for this design after you generate

the IP Compiler for PCI Express. The directories includes the following files:

■

The IP Compiler for PCI Express design files, stored in <working_dir>.

■

The chaining DMA design example file, stored in the

<working_dir>\top_examples\chaining_dma directory. This design example tests

your generated IP Compiler for PCI Express variation. For detailed information

about this design example, refer to

Chapter 15, Testbench and Design Example

.

■

The simulation files for the chaining DMA design example, stored in the

<working_dir>\top_examples\chaining_dma\testbench directory. The Quartus II

software generates the testbench files if you turn on Generate simulation model

on the EDA tab while generating the IP Compiler for PCI Express.

0

Figure 2–5. Directory Structure for IP Compiler for PCI Express and Testbench

Notes to

(1) The chaining_dma directory contains the Quartus II project and settings files.

(2) <variation>_plus.v is only available for the hard IP implementation.

<working_dir>

<variation>.v = top.v, the parameterized PCI Express IP Core

<variation>.sdc = top.sdc, the timing constraints file

<variation>.tcl = top.tcl, general Quartus II settings

<variation>_examples = top_examples

ip_compiler_for_pci_express-library

contains local copy of the pci express library files needed for

simulation, or compilation, or both

Testbench and

Design Example

Files

IP Compiler for

PCI Express

Files

Includes testbench and incremental compile directories

common

chaining_dma, files to implement the chaining DMA

top_example_chaining_top.qpf, the Quartus II project file

top_example_chaining_top.qsf, the Quartus II settings file

<variation>

_plus

.v = top_plus.v,

the parameterized PCI Express IP Core including reset and

calibration circuitry

testbench, scripts to run the testbench

runtb.do, script to run the testbench

<variation>_chaining_testbench = top_chaining_testbench.v

altpcietb_bfm_driver_chaining.v , provides test stimulus

Simulation and

Quartus II

Compilation

(1) (2)