Altera IP Compiler for PCI Express User Manual

Page 130

5–44

Chapter 5: IP Core Interfaces

Avalon-MM Application Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

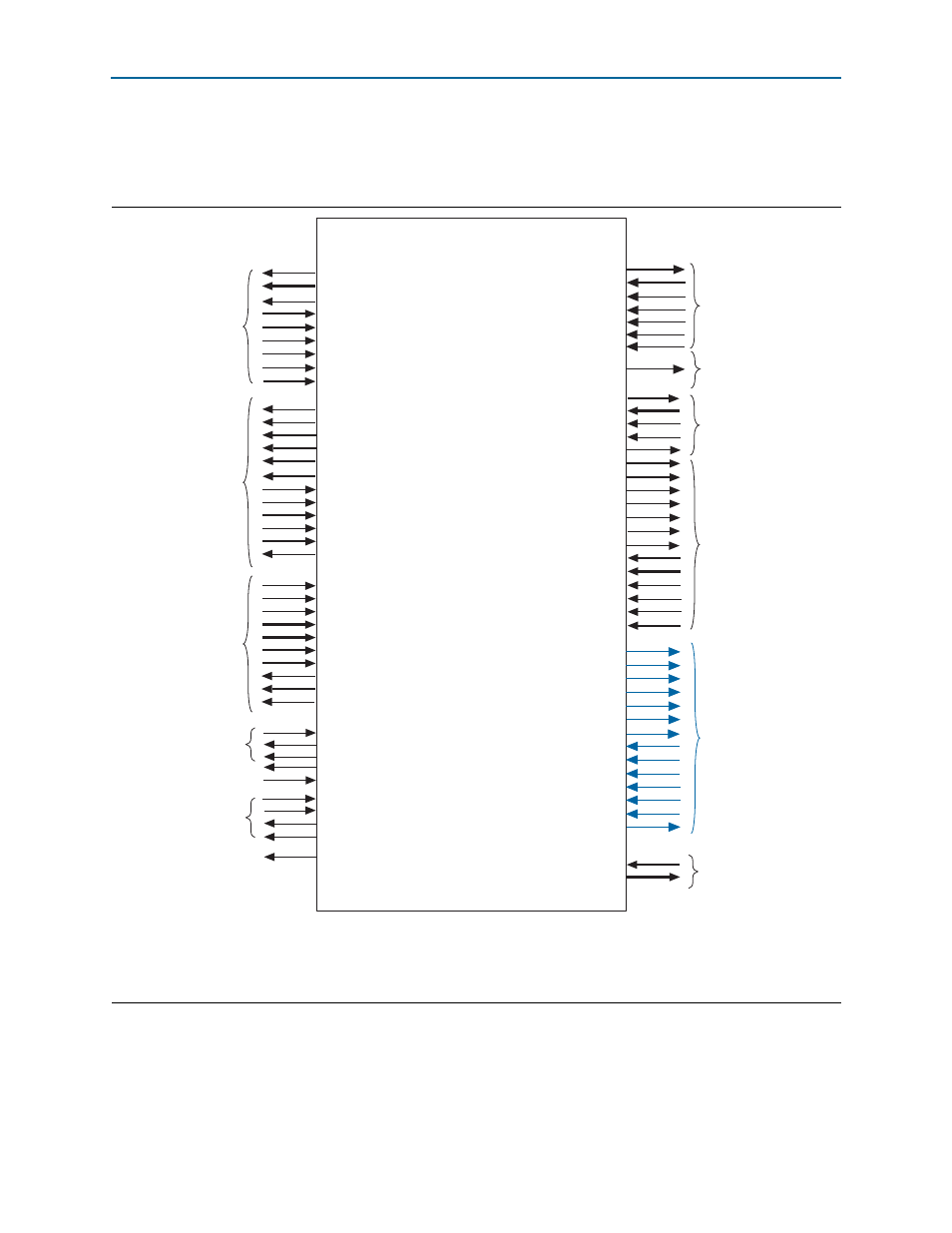

shows all the signals of a full-featured IP Compiler for PCI Express. Your

parameterization may not include some of the ports. The Avalon-MM signals are

shown on the left side of this figure.

Figure 5–36. Signals in the Soft or Hard Full-Featured IP Core with Avalon-MM Interface

Notes to

:

(1) Available in Stratix IV GX devices. For Stratix IV GX devices, <n> = 16 for ×1 and ×4 IP cores and <n> = 33 in the ×8 IP core.

(2) Available in Stratix IV GX devices. For Stratix IV GX reconfig_togxb, <n> = 3.

(3) Signals in blue are for simulation only.

tx_out0,...,tx_out3

busy_altgxb_reconfig

fixedclk_serdes

rx_in0,...,rx_in3

pipe_mode

xphy_pll_areset

xphy_pll_locked

txdatak

<n>

_ext[1:0]

txdata

<n>

_ext[15:0]

txdetectrx_ext

txelectidle

<n>

_ext

rxpolarity

<n>

_ext

txcompl

<n>

_ext

powerdown

<n>

_ext[1:0]

rxdata

<n>

_ext[15:0]

rxdatak

<n>

_ext[1:0]

rxvalid

<n>

_ext

phystatus_ext

rxelectidle

<n>

_ext

rxstatus0_ext[2:0]

txdatak0_ext

txdata0_ext[7:0]

txdetectrx_ext

txelectidle0_ext

rxpolarity0_ext

txcompl0_ext

powerdown0_ext[1:0]

rxdata0_ext[7:0]

rxdatak0_ext

rxvalid0_ext

phystatus_ext

rxelectidle0_ext

rxstatus0_ext[2:0]

rate_ext

1-Bit Serial

Soft IP

Implementation

16-Bit PIPE

for x1 and x4

(Repeat for lanes

1-3 in x4)

CraIrq_o

CraReadData_o[31:0]

CraWaitRequest_o

CraByteEnable_i[3:0]

CraChipSelect_i

CraAddress_i[11:0]

CraRead_i

CraWrite_i

CraWriteData_i[31:0]

RxmIrqNum_i[5:0]

RxmIrq_i

RxmReadDataValid_i

RxmWaitRequest_i

RxmAddress_o[31:0]

RxmReadData_i[63:0]

RxmBurstCount_o[9:0]

RxmByteEnable_o[7:0]

RxmWrite_o

RxmRead_o

RxmWriteData_o[63:0]

RxmResetRequest_o

TxsWriteData_i[63:0]

TxsRead_i

TxsChipSelect_i

TxsWaitRequest_o

TxsWrite_i

TxsByteEnable_i[7:0]

TxsBurstCount_i[9:0]

TxsReadDataValid_o

TxsReadData_o[63:0]

TxsAddress_i[WIDTH-1:0]

32-Bit

Avalon-MM

CRA

Slave Port

64-Bit

Avalon-MM Rx

Master Port

64-Bit

Avalon-MM Tx

Slave Port

reset_n

reset_status

AvlClk_i

Clock

Reset &

Status

clk125_out

refclk

pcie_rstn

suc_spd_neg

IP Compiler for PCI Express

with Avalon-MM Interface Signals

Hard IP

Implementation

Simulation

Only

8-Bit PIPE

clk250_out

clk500_out

tl_cfg_{add, ctl, ctl_wr, sts, sts_wr}

Test

Interface

test_out[511 or 127 or 63 or 8:0]

test_in[31:0]

(test_out is optional)

reconfig_fromgxb[

<n>

:0]

reconfig_togxb[

<n>

:0]

reconfig_clk

cal_blk_clk

gxb_powerdown

Transceiver

Control

rc_pll_locked

Transceiver

Status

(1)

(2)

(3)