Error reporting and data poisoning, Fcpe) – Altera IP Compiler for PCI Express User Manual

Page 207

Chapter 12: Error Handling

12–5

Error Reporting and Data Poisoning

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Error Reporting and Data Poisoning

How the endpoint handles a particular error depends on the configuration registers of

the device.

f

for a description of the device

signaling and logging for an endpoint.

The IP core implements data poisoning, a mechanism for indicating that the data

associated with a transaction is corrupted. Poisoned transaction layer packets have

the error/poisoned bit of the header set to 1 and observe the following rules:

■

Received poisoned transaction layer packets are sent to the application layer and

status bits are automatically updated in the configuration space. In PCI Express

1.1, this is treated as an advisory error.

■

Received poisoned configuration write transaction layer packets are not written in

the configuration space.

■

The configuration space never generates a poisoned transaction layer packet; the

error/poisoned bit of the header is always set to 0.

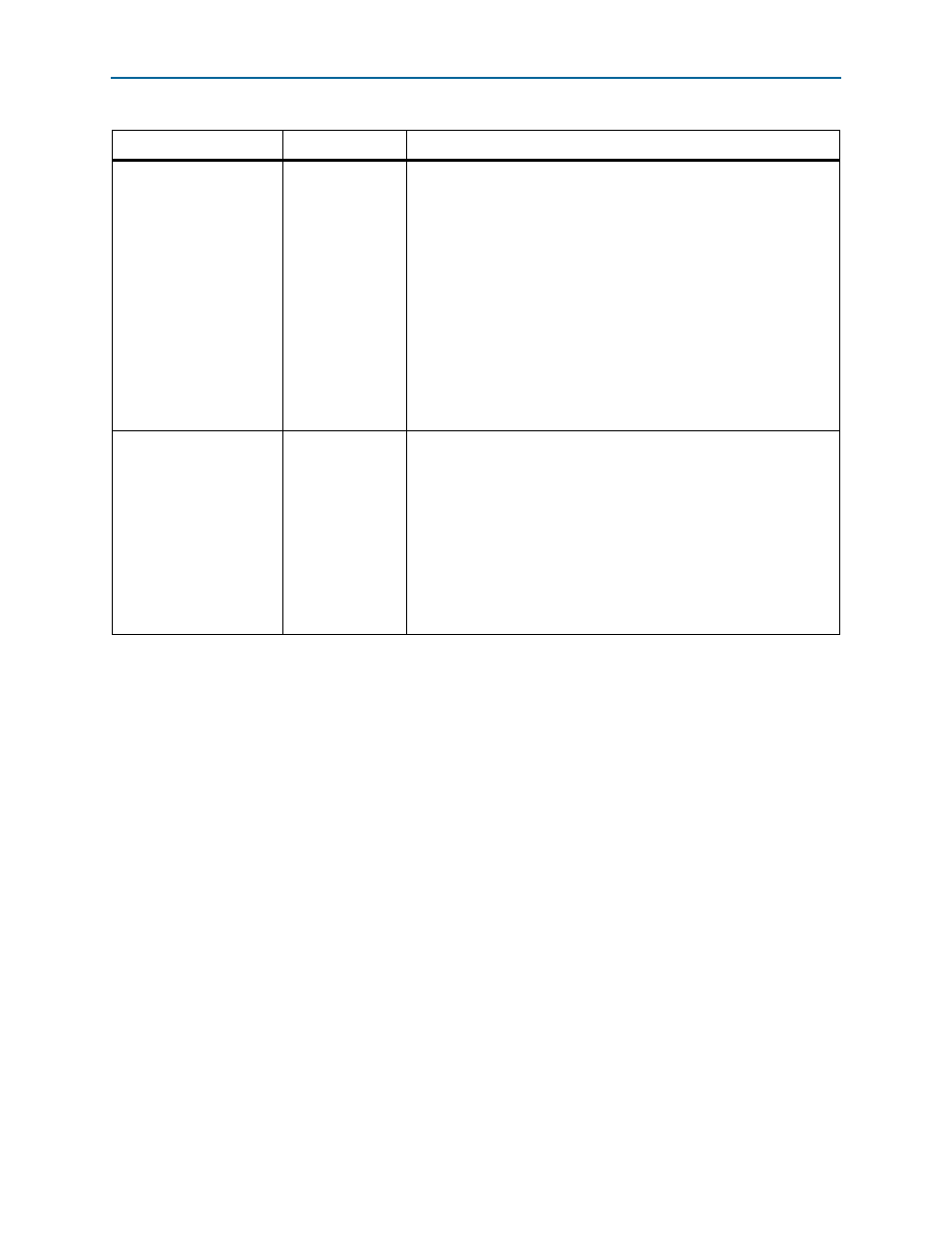

Malformed TLP

Uncorrectable

(fatal)

This error is caused by any of the following conditions:

■

The data payload of a received transaction layer packet exceeds the

maximum payload size.

■

The TD field is asserted but no transaction layer packet digest exists,

or a transaction layer packet digest exists but the TD bit of the PCI

Express request header packet is not asserted.

■

A transaction layer packet violates a byte enable rule. The IP core

checks for this violation, which is considered optional by the PCI

Express specifications.

■

A transaction layer packet in which the type and length fields do not

correspond with the total length of the transaction layer packet.

■

A transaction layer packet in which the combination of format and

type is not specified by the PCI Express specification.

Malformed TLP

(continued)

Uncorrectable

(fatal)

■

A request specifies an address/length combination that causes a

memory space access to exceed a 4 KByte boundary. The IP core

checks for this violation, which is considered optional by the PCI

Express specification.

■

Messages, such as Assert_INTX, power management, error

signaling, unlock, and Set_Slot_power_limit, must be transmitted

across the default traffic class.

■

A transaction layer packet that uses an uninitialized virtual channel.

The IP core deletes the malformed TLP; it is not presented to the

application layer.

Note to

:

(1) Considered optional by the

.

Table 12–4. Errors Detected by the Transaction Layer (Part 3 of 3)

Error

Type

Description