Priority given elsewhere, Figure b–18 – Altera IP Compiler for PCI Express User Manual

Page 339

Chapter :

B–21

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

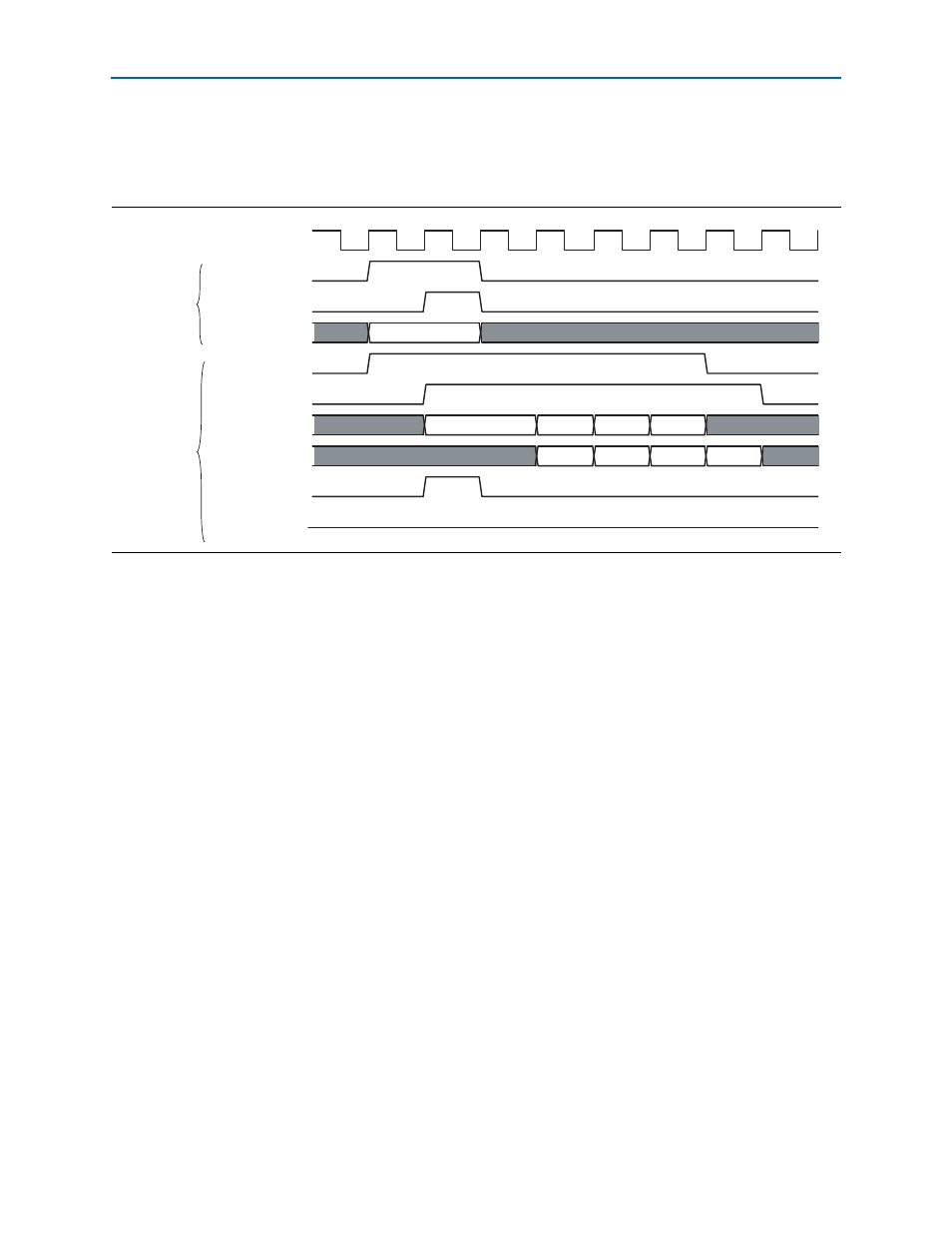

In clock cycle 3, the IP core inserts a wait state because the memory write 64-bit

transaction layer packet request has a 4-DWORD header. In this case, tx_dv could

have been sent one clock cycle later.

Priority Given Elsewhere

In this example, the application transmits a 64-bit memory write transaction of 8

DWORDS. Address bit 2 is set to 0. The transmit path has a 3-deep, 64-bit buffer to

handle back-to-back transaction layer packets as fast as possible, and it accepts the

tx_desc

and first tx_data without delay. Refer to

.

Figure B–18. TX Inserting Wait States because of 4-DWORD Header Waveform

clk

tx_req

tx_ack

tx_desc[127:0]

tx_dfr

tx_dv

tx_data[63:32]

tx_data[63:32]

tx_ws

tx_err

Descriptor

Signals

Data

Signals

DW 0

DW 2

DW 4

DW 6

DW 1

DW 3

DW 5

DW 7

1

2

3

4

5

6

7

8

9