Altera IP Compiler for PCI Express User Manual

Page 320

B–2

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

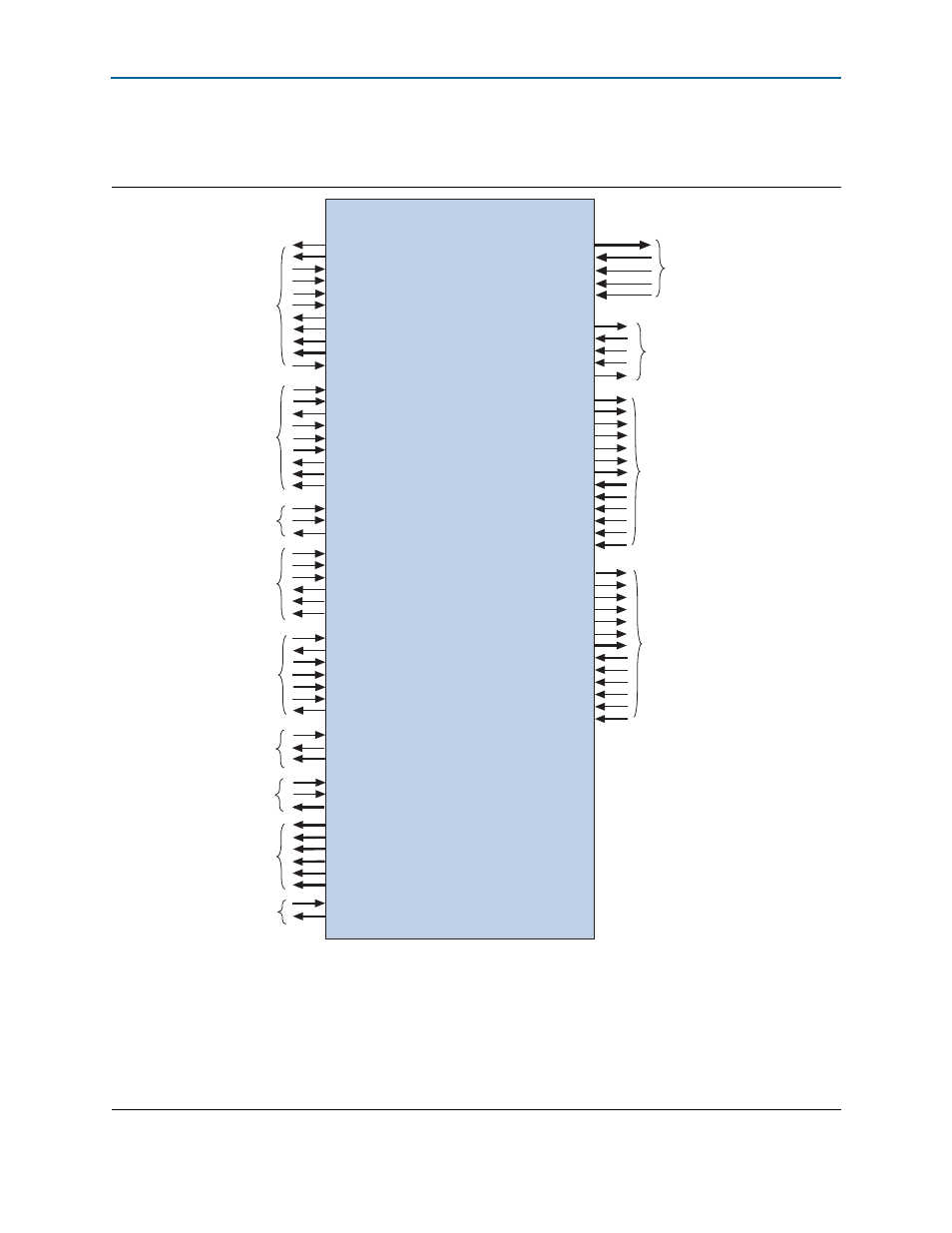

shows all the signals for IP Compiler for PCI Express using the

descriptor/data interface.

Figure B–2. IP Compiler for PCI Express with Descriptor Data Interface

Notes to

(1) clk125_in replaced with clk250_in for ×8 IP core

(2) clk125_out replaced with clk250_out for ×8 IP core

(3) srst and crst removed for ×8 IP core

(4) test_out[511:0] replaced with test_out[127:0] for ×8 IP core

(5) Available in Stratix II GX, Stratix IV GX, Arria GX, and HardCopy IV GX devices. The reconfig_fromgxb is a single wire for Stratix II GX and

Arria GX devices. For Stratix IV GX devices, <n> = 16 for ×1 and ×4 IP cores and <n> = 33 in the ×8 IP core.

(6) Available in Stratix II GX, Stratix IV GX, Arria GX, and HardCopy IV GX devices. For Stratix II GX and Arria GX reconfig_togxb, <n> = 2. For

Stratix IV GX reconfig_togxb, <n> = 3.

rx_req<n>

rx_desc

<n>[135:0]

rx_ack

<n>

rx_abort

<n>

rx_retry

<n>

rx_mask

<n>

rx_dfr

<n>

rx_dv

<n>

rx_data

<n>[63:0]

rx_be

<n>[7:0]

rx_ws

<n>

tx_req

<n>

tx_desc

<n>

tx_ack

<n>

tx_dfr

<n>

tx_dv

<n>

tx_data

<n>[63:0]

tx_ws

<n>

tx_cred

<n>[21:0]

tx_err

<n> (x1 and x4 only)

refclk

clk125_in

clk125_out

npor

srst

crst

12_exit

hotrst_exit

dlup_exit

app_msi_req

app_msi_ack

ack_msi_tc[2:0]

msi_num[4:0]

pex_msi_num[4:0]

app_int_sts

app_int_ack

pme_to_cr

pme_to_sr

cfg_pmcsr[31:0]

cpl_err[2:0]

cpl_pending

ko_cpl_spc_vcn[19:0]

cfg_tcvcmap[23:0]

cfg_busdev[12:0]

cfg_prmcsr[31:0]

cfg_devcsr[31:0]

cfg_linkcsr[31:0]

cfg_msicsr[15:0]

test_in[31:0]

test_out[511:0]

Signals in the IP Compiler for PCI Express

with Descriptor/Data Interface

1-Bit Serial

tx[7:0]

rx[7:0]

pipe_mode

xphy_pll_areset

xphy_pll_locked

txdata0_ext[15:0]

txdatak0_ext[1:0]

txdetectrx0_ext

txelecidle0_ext

txcompliance0_ext

rxpolarity0_ext

powerdown0_ext[1:0]

rxdata0_ext[15:0]

rxdatak0_ext[1:0]

rxvalid0_ext

phystatus0_ext

rxelecidle0_ext

rxstatus0_ext[2:0]

16-Bit PIPE for x1 and x4

(Repeated for Lanes 1 - 3

in the x4 MegaCore Function)

Transmit Data

Path (for VC<n>)

Receive Data

Path (for VC<n>)

Power Management

Interrupt

Clock

Reset

Configuration

Completion Interface

Test Interface

txdata0_ext[7:0]

txdatak0_ext

txdetectrx0_ext

txelecidle0_ext

txcompliance0_ext

rxpolarity0_ext

powerdown0_ext[1:0]

rxdata0_ext[7:0]

rxdatak0_ext

rxvalid0_ext

phystatus0_ext

rxelecidle0_ext

rxstatus0_ext[2:0]

8-Bit PIPE for x8

(Repeated for Lanes 1 - 7

in the x8 MegaCore Function)

(1)

(2)

(3)

(3)

(4)

(5)

(6)

reconfig_fromgxb[

<n>:0]

reconfig_togxb[

<n>:0]

reconfig_clk

cal_blk_clk

gxb_powerdown

Transceiver

Control