Error asserted and transmission is nullified – Altera IP Compiler for PCI Express User Manual

Page 342

B–24

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

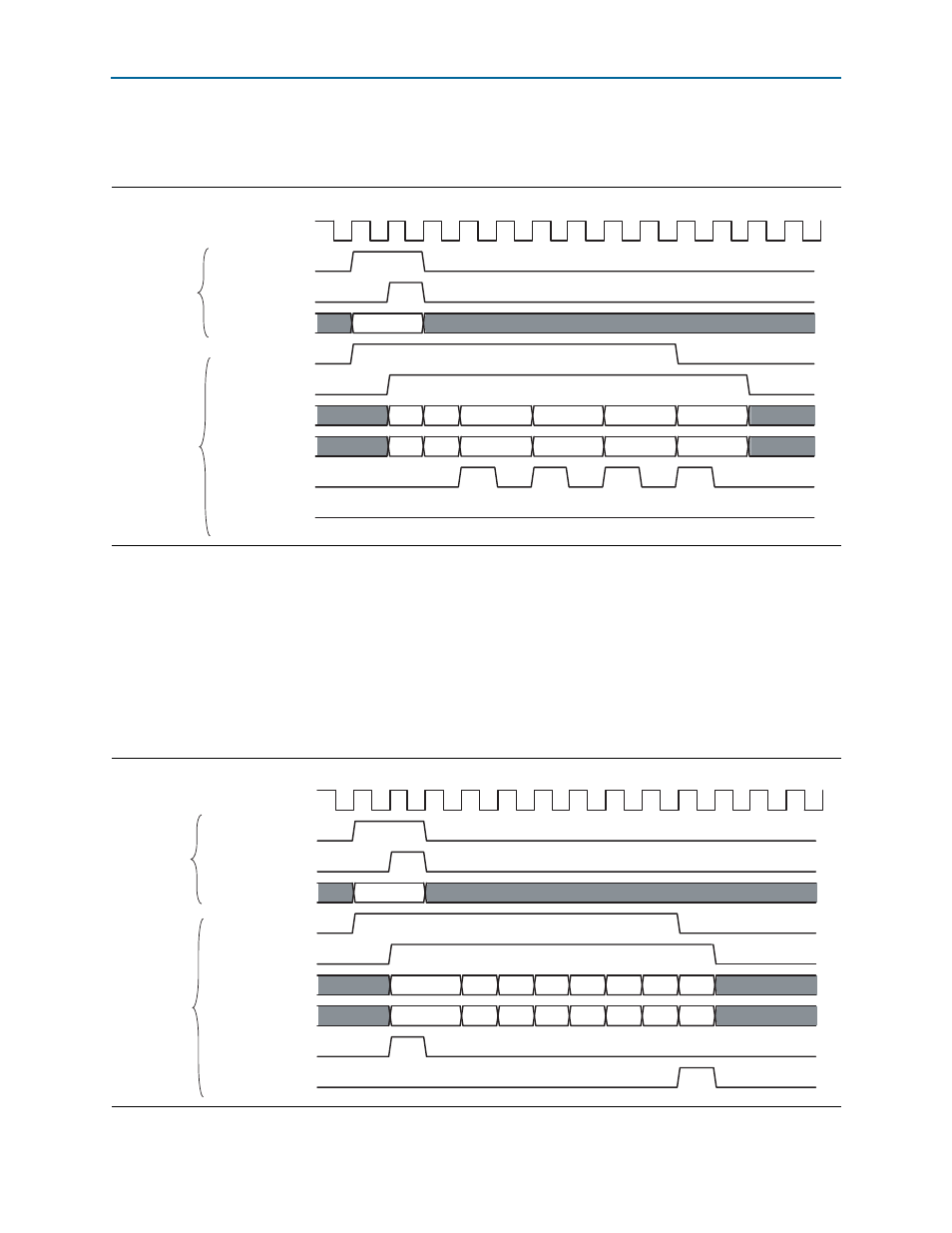

In clock cycles 5, 7, 9, and 11, the IP core inserts wait states to throttle the flow of

transmission.

Error Asserted and Transmission Is Nullified

In this example, the application transmits a 64-bit memory write transaction of 14

DWORDS. Address bit 2 is set to 0. Refer to

In clock cycle 12, tx_err is asserted which nullifies transmission of the transaction

layer packet on the link. Nullified packets have the LCRC inverted from the

calculated value and use the end bad packet (EDB) control character instead of the

normal END control character.

Figure B–21. TX Multiple Wait States that Throttle Data Transmission Waveform

clk

tx_req

tx_ack

tx_desc[127:0]

tx_dfr

tx_dv

tx_data[63:32]

tx_data[31:0]

tx_ws

tx_err

MEMWR64

DW 1

DW 3

DW 5

DW 7

DW 9

DW 11

DW 0

DW 2

DW 4

DW 6

DW 8

DW 10

1

2

3

4

5

6

7

9

8

10

11

12

14

13

Descriptor

Signals

Data

Signals

Figure B–22. TX Error Assertion Waveform

clk

tx_req

tx_ack

tx_desc[127:0]

tx_dfr

tx_dv

tx_data[63:32]

tx_data[63:32]

tx_ws

tx_err

MEMWR64

DW 1

DW 3

DW 5

DW 7

DW 9

DW B

DW D

DW F

DW 0

DW 2

DW 4

DW 6

DW 8

DW A

DW C

DW E

1

2

3

4

5

6

7

9

8

10

11

12

14

13

Descriptor

Signals

Data

Signals