Altera IP Compiler for PCI Express User Manual

Page 146

5–60

Chapter 5: IP Core Interfaces

Test Signals

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

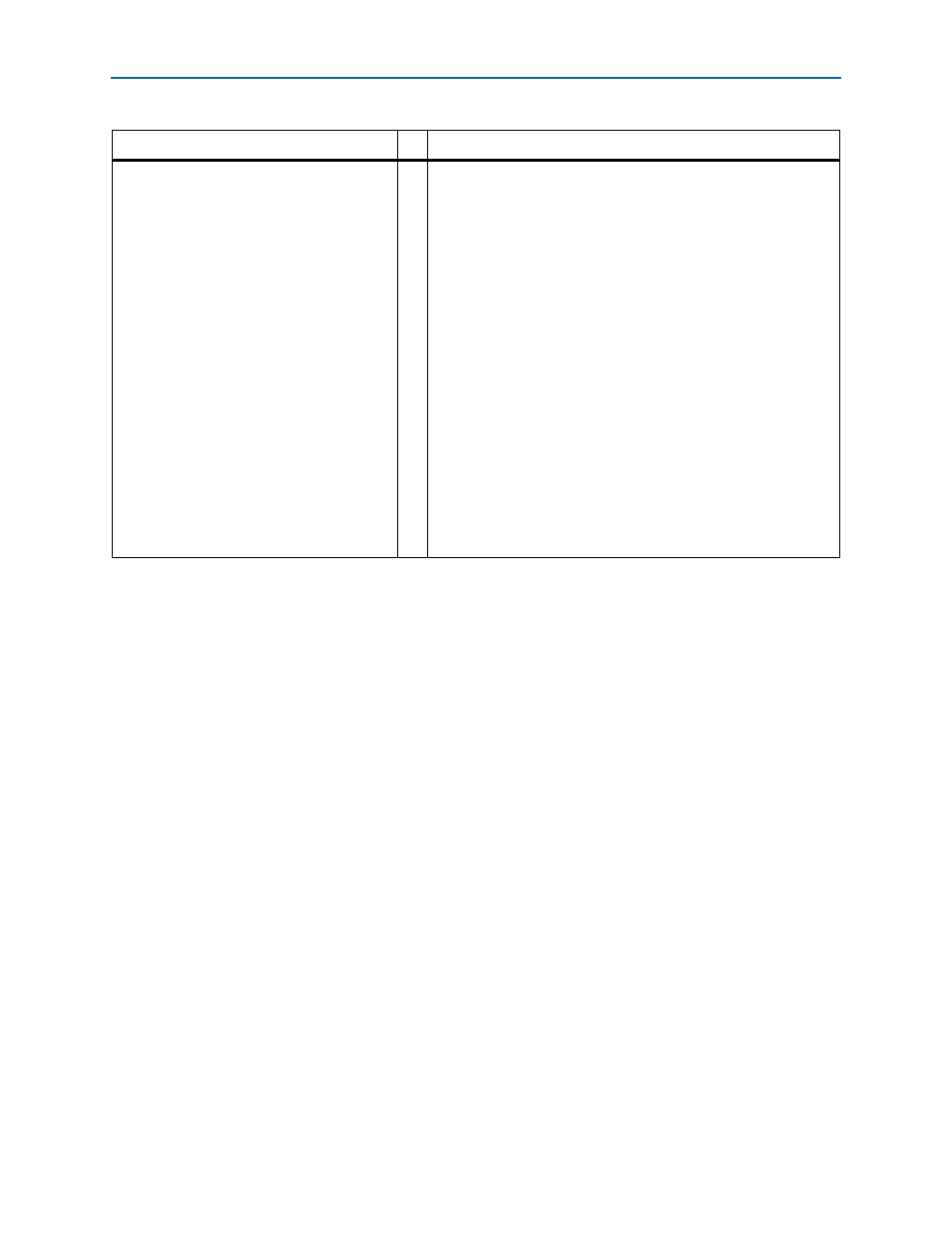

The test_out bus allows you to monitor the PIPE interface.

If you select the 9-bit test_out bus width, a subset of the 64-bit test

bus is brought out as follows:

test_out[63:0]

or [8:0]

O

■

bits [8:5] = test_out[28:25]–Reserved.

■

bits [4:0] = test_out[4:0]–txdata[3:0]

The following bits are defined:

■

[7:0]–txdata

■

[8]–txdatak

■

[9]–txdetectrx

■

[10]–txelecidle

■

[11]–txcompl

■

[12]–rxpolarity

■

[14:13]–powerdown

■

[22:15]–rxdata

■

[23]–rxdatak

■

[24]–rxvalid

■

[63:25]–Reserved.

Notes to

:

(1) All signals are per lane.

(2) Refer to

“PIPE Interface Signals” on page 5–57

for definitions of the PIPE interface signals.

Table 5–33. Test Interface Signals—Hard IP Implementation (Part 2 of 2)

Signal

I/O

Description