Variation_name>_icm partition – Altera IP Compiler for PCI Express User Manual

Page 346

B–28

Chapter :

Incremental Compile Module for Descriptor/Data Examples

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

<variation_name>_icm Partition

When you generate an IP Compiler for PCI Express, the parameter editor generates

module <variation_name>_icm in the subdirectory

<variation_name>_examples\common\incremental_compile_module

, as a

wrapper file that contains the IP core and the ICM module. (Refer to

Your application connects to this wrapper file. The wrapper interface resembles the IP

Compiler for PCI Express interface, but replaces it with an Avalon-ST interface. (Refer

to

.)

1

The wrapper interface omits some signals from the IP core to maximize circuit

optimization across the partition boundary. However, all of the IP core signals are still

available in the IP core instance and can be wired to the wrapper interface by editing

the <variation_name>_icm file as required.

By setting this wrapper module as a design partition, you can preserve timing of the

IP core using the incremental synthesis flow.

describes the <variation_name>_icm interfaces.

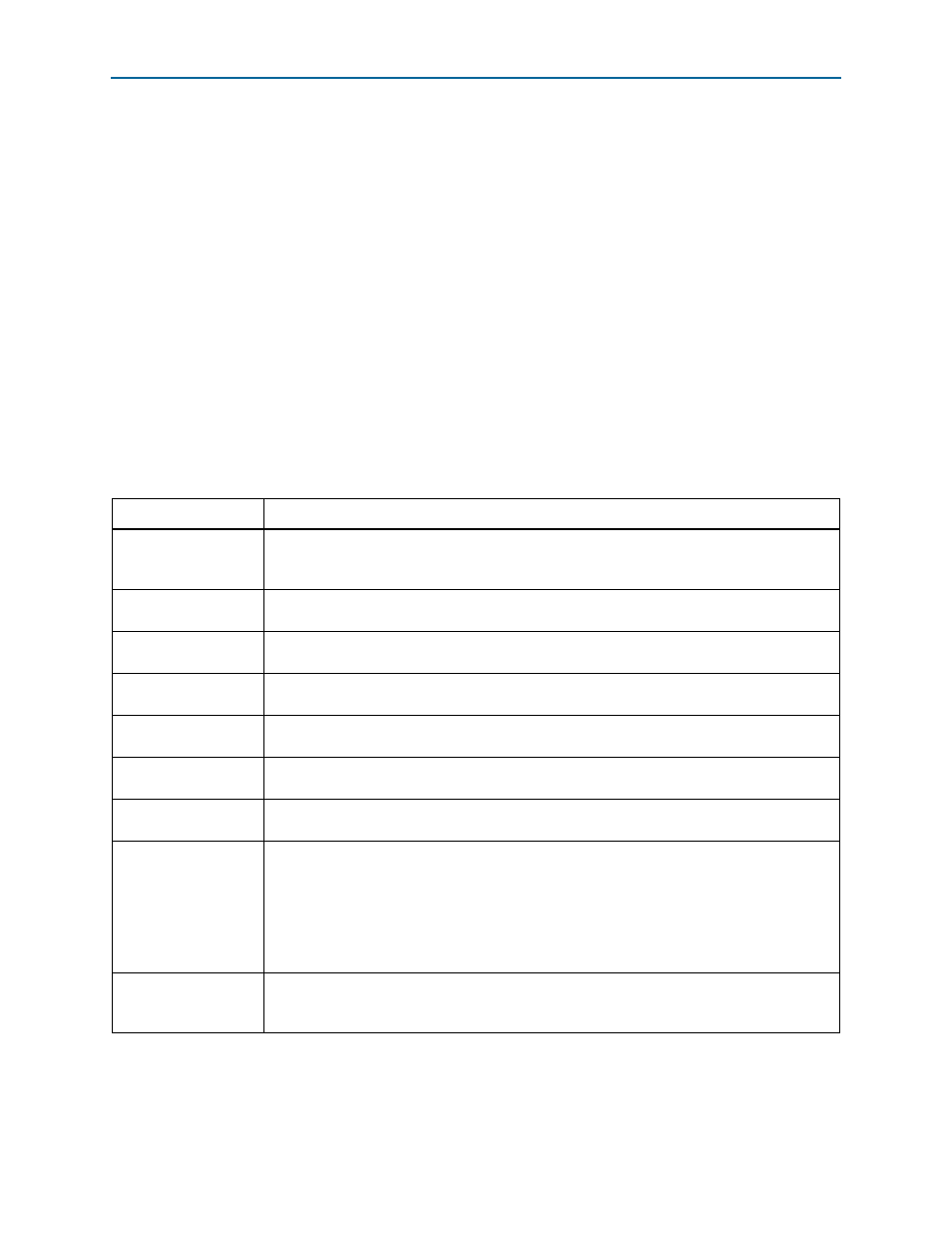

Table B–12. <variation_name>_icm Interface Descriptions

Signal Group

Description

Transmit Datapath

ICM Avalon-ST TX interface. These signals include tx_stream_valid0, tx_stream_data0,

tx_stream_ready0

, tx_stream_cred0, and tx_stream_mask0. Refer to

for details.

Receive Datapath

ICM interface. These signals include rx_stream_valid0, rx_stream_data0,

rx_stream_ready0

, and rx_stream_mask0. Refer to

for details.

Part of ICM sideband interface. These signals include cfg_busdev_icm, cfg_devcsr_icm, and

cfg_linkcsr_icm

.

Completion interfaces

Part of ICM sideband interface. These signals include cpl_pending_icm, cpl_err_icm,

pex_msi_num_icm

, and app_int_sts_icm. Refer to

Interrupt

ICM Avalon-ST MSI interface. These signals include msi_stream_valid0, msi_stream_data0,

and msi_stream_ready0. Refer to

for details.

Test Interface

Part of ICM sideband signals; includes test_out_icm. Refer to

details.

Global Interface

IP core signals; includes refclk, clk125_in, clk125_out, npor, srst, crst, ls_exit,

hotrst_exit

, and dlup_exit. Refer to

for details.

PIPE Interface

IP core signals; includes tx, rx, pipe_mode, txdata0_ext, txdatak0_ext,

txdetectrx0_ext

, txelecidle0_ext, txcompliance0_ext, rxpolarity0_ext,

powerdown0_ext

, rxdata0_ext, rxdatak0_ext, rxvalid0_ext, phystatus0_ext,

rxelecidle0_ext

, rxstatus0_ext, txdata0_ext, txdatak0_ext, txdetectrx0_ext,

txelecidle0_ext

, txcompliance0_ext, rxpolarity0_ext, powerdown0_ext,

rxdata0_ext

, rxdatak0_ext, rxvalid0_ext, phystatus0_ext, rxelecidle0_ext, and

rxstatus0_ext

for details.

Maximum Completion

Space Signals

This signal is ko_cpl_spc_vc<n>, and is not available at the <variation_name>_icm ports

.

Instead, this static signal is regenerated for the user in the <variation_name>_example_pipen1b

module.

Note to

:

(1) Cfg_tcvcmap is available from the ICM module, but not wired to the <variation_name>_icm ports. Refer to

for

details.