Altera IP Compiler for PCI Express User Manual

Page 299

Chapter 16: Qsys Design Example

16–11

Specifying Address Assignments

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

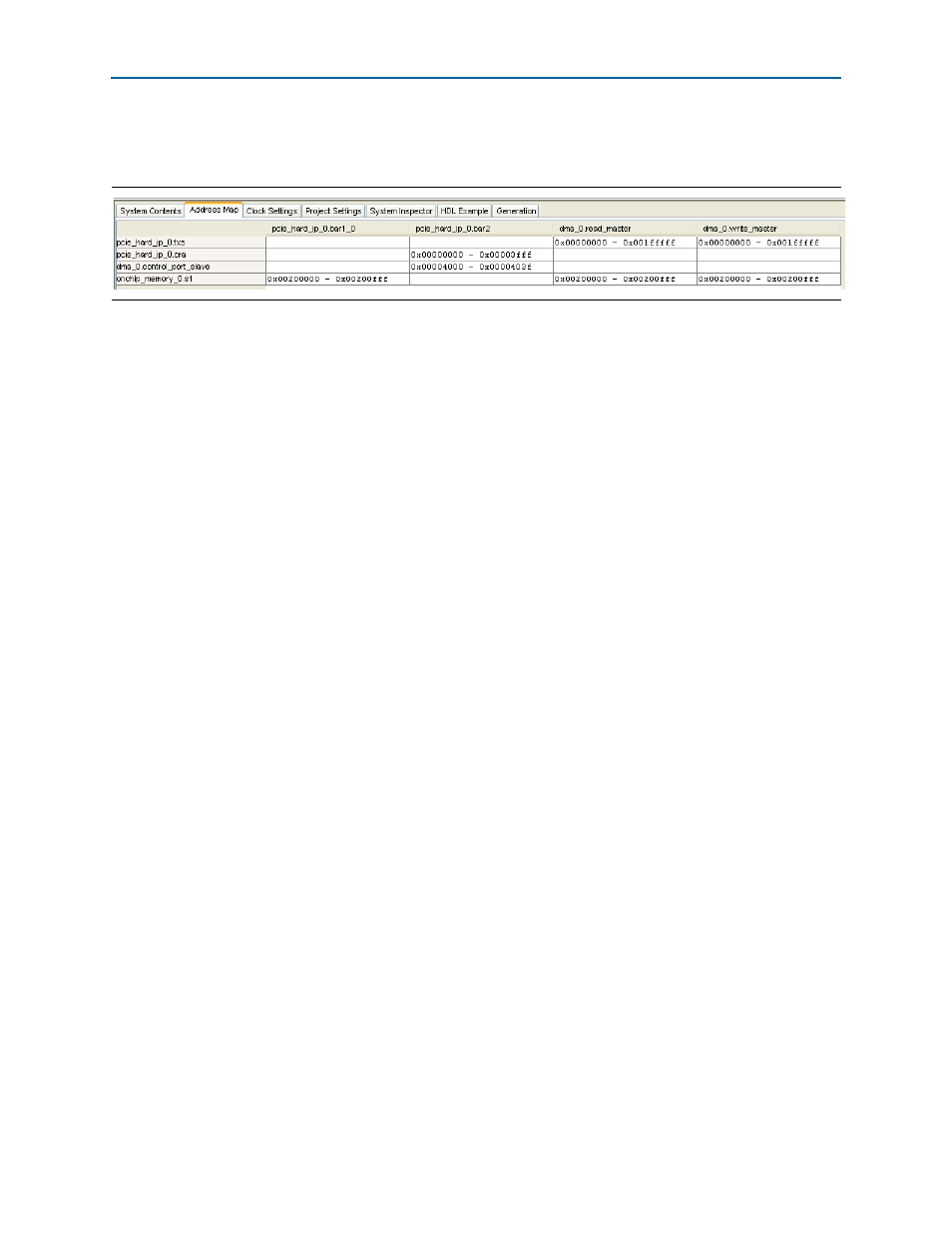

shows the Address Map tab of the Qsys system after you assign the base

PCI Express requests to an address in the range assigned to BAR1:0 are converted to

Avalon-MM read and write transfers to onchip_memory_0. PCI Express requests to an

address in the range assigned to BAR2 are converted to Avalon-MM read and write

transfers to the IP Compiler for PCI Express cra slave port or to the DMA controller

control_port_slave

port.

The pcie_hard_ip_0 cra slave port is accessible at offsets 0x0000000–0x0003FFF from

the programmed BAR2 base address. The DMA control_port_slave is accessible at

offsets 0x00004000 through 0x0000403F from the programmed BAR2 base address.

Refer to

“PCI Express-to-Avalon-MM Address Translation” on page 4–21

additional information about this address mapping.

For Avalon-MM accesses directed to the pcie_hard_ip_0 txs Avalon-MM Slave port,

Avalon-MM address bits 19-0 pass to the PCI Express address unchanged because you

selected a 1 MByte or 20–bit address page size. Bit 20 selects which one of the two

address translation table entries provides the upper bits of the PCI Express address.

Avalon-MM address bits [31:21] select the txs Avalon-MM Slave port. Refer to section

“Avalon-MM-to-PCI Express Address Translation” on page 4–20

for additional

information about this address mapping.

Figure 16–3. Qsys System Address Map